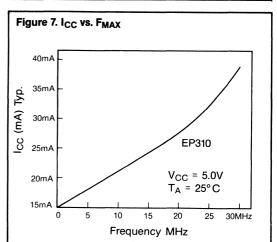

USER-CONFIGURABLE LOGIC

**DATABOOK**

The following are trademarks of Altera Corporation: A+PLUS, LogicMap, LogiCaps, MacroMunching, TURBO-BIT, SALSA, ADLIB, SAM+PLUS, PLDS-SAM, PLS-SAM, SAMSIM, ASMILE, PLDS2, PLS4, PLS2, PLCAD, PLE, ASAP, EP300, EP310, EP512, EP600, EP610, EP900, EP910, EP1200, EP1210, EP1800, EP1810, EPS448, EPB1400, EPB2001, EPB2002, EPM5016, EPM5024. EPM5032, EPM5064, EPM5127, EPM5128, SAM, BUSTER, MCMAP, MAX, and MAX+PLUS, A+PLUS design elements and Mnemonics are Altera Corporation copyright. IBM is a registered trademark of International Business Machines, Inc. PS/2 and Micro Channel are trademarks of International Business Machines, Inc. CHMOS is a trademark of Intel Corporation. PC-CAPS is a tradmark of Personal CAD Systems Inc. Dash is a trademark of FutureNet Corporation. PAL is a trademark of Monolithic Memories Inc. MS-DOS is a trademark of Microsoft Corporation. WordStar is a trademark of MicroPro Corporation. Altera reserves the right to make changes in the devices or the device specifications identified in this document without notice. Altera advises its customers to obtain the latest version of device specifications to verify, before placing orders, that the information being relied upon by the customer is current. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty. Testing and other quality control techniques are utilized to the extent Altera deems such testing necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed. In the absence of written agreement to the contrary, Altera assumes no liability for Altera applications assistance, customers product design, or infringement of patents or copyrights of third parties by or arising from use of semiconductor devices described herein. Nor does Altera warrant or represent that any patent right, copyright, or other intellectual property right of Altera covering or relating to any combination, machine, or process in which such semiconductor devices might be or are used.

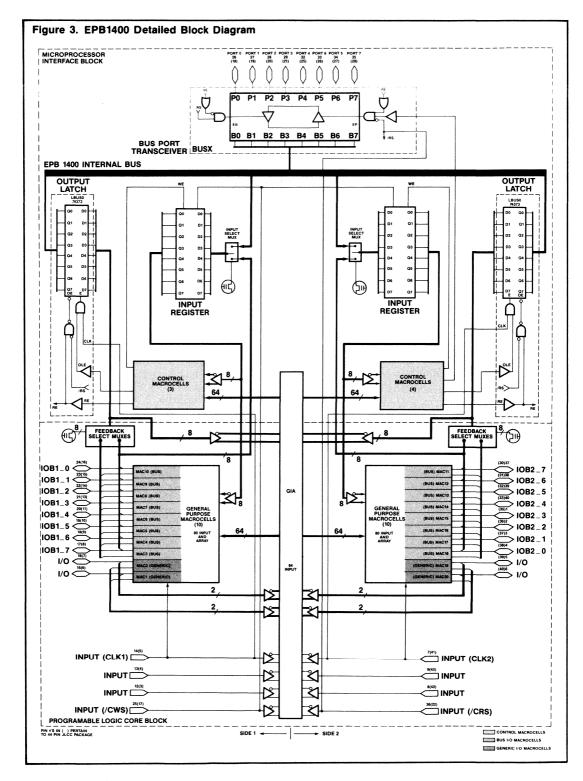

Altera's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of Altera Corporation. As used herein:

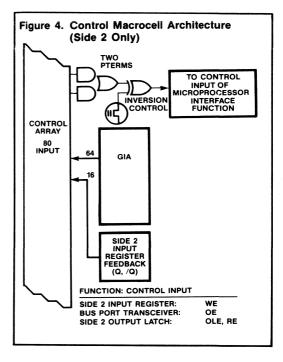

- Life support devices or systems are devices or systems which,

(a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

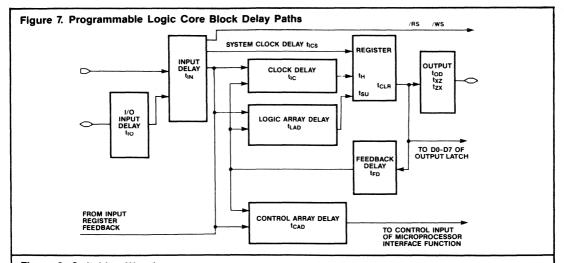

ALTERA cannot assume any responsibility for any circuits shown or represented that they are free from patent infringement.

Products contained within are covered by one or more of the following U. S. patents: #4,609,986; #4,677,318; #4,617,479; #4,713,792; #4,328,565; #4,361,847; #4,409,723; #4,639,893; #4,649,520; and the following foreign patents: England: #2,072,384; #2,073,487; West Germany: #3,103,160; and Japan: #1,279,100. Additional Patents Pending.

Copyright ©1985, 1986, 1987, 1988 ALTERA Corporation 0888103 DFGG

ALTERA CORPORATION 3525 MONROE STREET, P.O. BOX 58163 SANTA CLARA, CA 95052-8163 (408) 984-2800

| SECTION 1: Introduction to Altera   | Page No. |                                       |

|-------------------------------------|----------|---------------------------------------|

|                                     |          |                                       |

| ■ SECTION 1 TABLE OF CONTENTS       | 1        |                                       |

| ■ ALPHA-NUMERIC INDEX               | 2        |                                       |

| ■ INTRODUCTION TO ALTERA            | 3        |                                       |

| ALTERA EPLD DESIGN ENVIRONMENT      | 7        |                                       |

| ■ DEVICE SELECTOR GUIDE             | 8        |                                       |

| <br>SECTION 2: EPLD Datasheets      | Page No. | · · · · · · · · · · · · · · · · · · · |

|                                     |          |                                       |

| ■ SECTION 2 TABLE OF CONTENTS       | 9        |                                       |

| ■ HIGH DENSITY EPLDs                | 10-36    |                                       |

| LOW DENSITY EPLDs                   | 37-80    |                                       |

| ■ FUNCTION SPECIFIC EPLDs           | 81-135   |                                       |

| ■ MULTIPLE ARRAY MATRIX (MAX) EPLDs | 136-161  |                                       |

| ■ DESIGN RECOMMENDATIONS            | 162      |                                       |

|                                     |          |                                       |

| <br>SECTION 3: Development Systems  | Page No. |                                       |

|                                     |          |                                       |

| ■ SECTION 3 TABLE OF CONTENTS       | 163      |                                       |

| ■ DEVELOPMENT SYSTEMS               | 165-171  |                                       |

| ■ DEVELOPMENT SOFTWARE              | 172-220  |                                       |

| PROGRAMMING HARDWARE                | 221-222  |                                       |

|                                     |          |                                       |

| SECTION 4: General Information      | Page No. |                                       |

|                                     |          |                                       |

| ■ SECTION 4 TABLE OF CONTENTS       | 223      |                                       |

| ■ APPLICATIONS LITERATURE           | 224-225  |                                       |

| ■ ORDERING INFORMATION              | 226      |                                       |

| ■ QUALITY PROGRAMS                  | 227-237  |                                       |

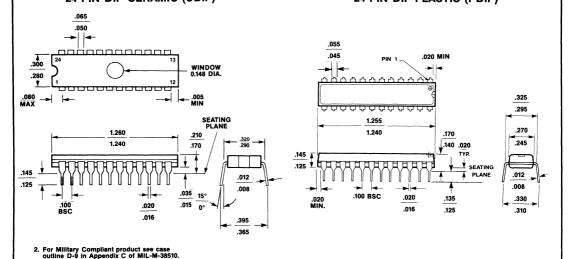

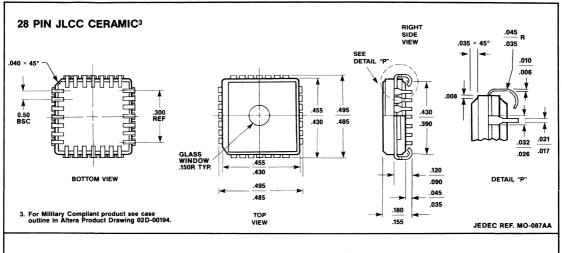

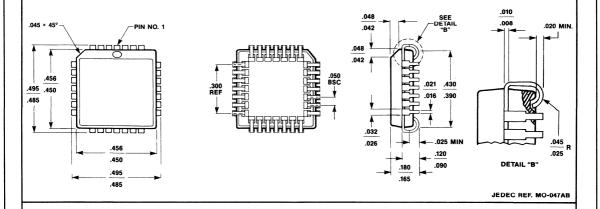

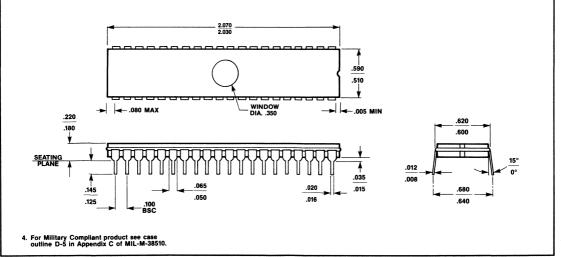

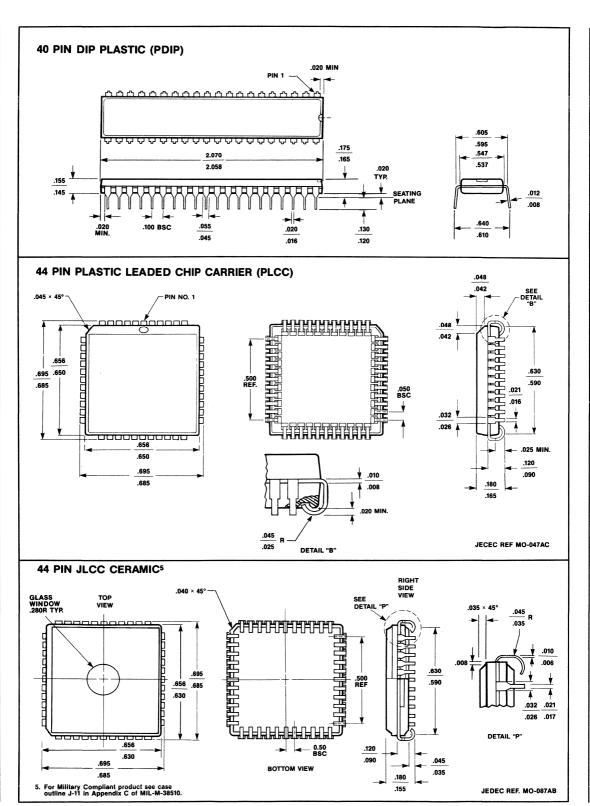

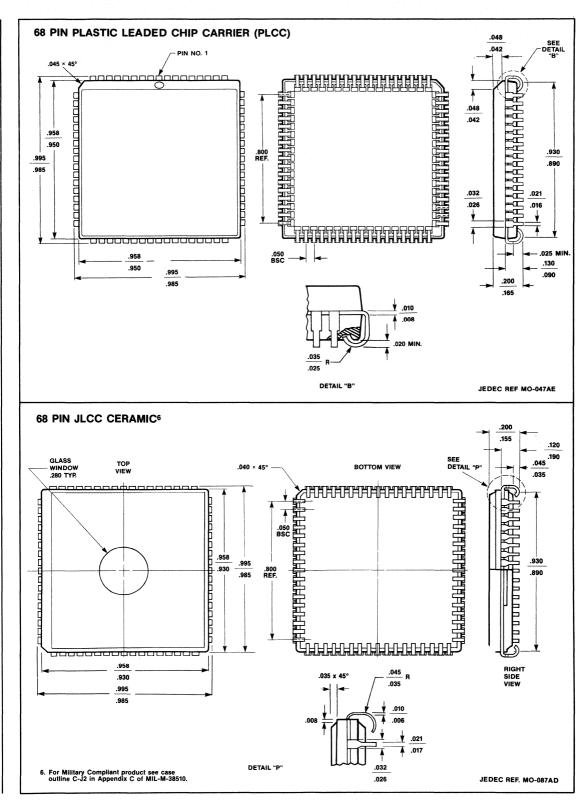

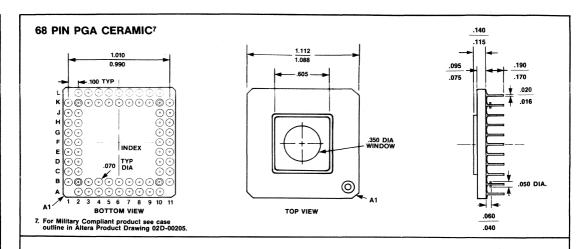

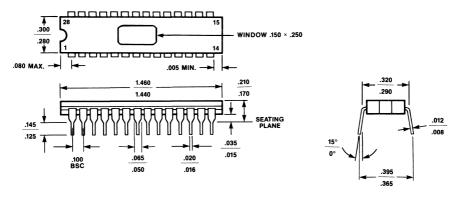

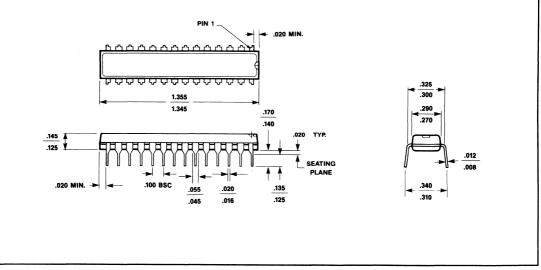

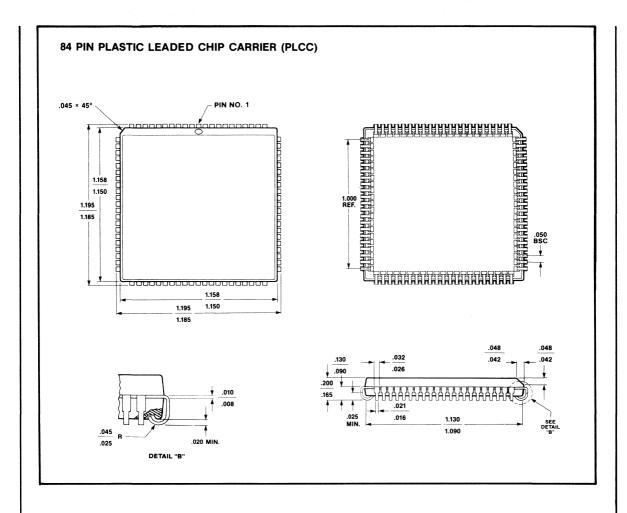

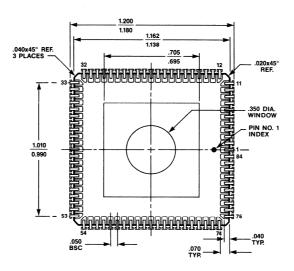

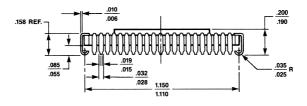

| ■ PACKAGE OUTLINES                  | 238-244  |                                       |

| ■ THERMAL DATA                      | 245      |                                       |

| ■ SALES OFFICES                     | 246-252  |                                       |

|                                     |          |                                       |

# HOW TO USE THIS DATABOOK

This databook provides technical datasheets for Altera EPLD and Development Tool products. If you are already familiar with Altera EPLDs and the associated design support versus other semicustom logic alternatives, you can go right to the product data in Section 2. On the other hand, if you're venturing into EPLDs or semicustom logic for the first time, you may choose to acquaint yourself with Section 1 which includes some brief history and a discussion of the technology issues and alternatives in the application specific market.

To place an order, go directly to the Appendices in Section 4 for ordering information, package outlines, or distributor locations.

If this databook doesn't answer your technical questions, please call our applications HOT-LINE (408) 984-2805 extension 102, and we will help you directly.

For Application Notes and design guideline information, refer to the Altera Applications Handbook.

| INTRODUCTION TO ALTERA         | PAGE NO. |  |

|--------------------------------|----------|--|

| Alpha-Numeric Index            | 3        |  |

| Altera EPLD Design Environment |          |  |

| Device Selector Guide          | 8        |  |

### **ALPHA-NUMERIC INDEX**

| EPLDs                                   |          | DEVELOPMENT TOOLS |      |  |  |  |

|-----------------------------------------|----------|-------------------|------|--|--|--|

| PRODUCT                                 | PAGE     | PRODUCT           | PAGE |  |  |  |

| EPB1400                                 | 81       | PLAESW            | 219  |  |  |  |

| EPB1400-2                               | 81       | PLDCAD-SUPREME    | 167  |  |  |  |

| EPB2001                                 | 118      | PLDS-ENCORE       | 166  |  |  |  |

| EPB2002                                 | 118      | PLDS-MAX          | 168  |  |  |  |

| EPM5016                                 | 146      | PLDS-MCMAP        | 170  |  |  |  |

| EPM5024                                 | 145      | PLDS-SAM          | 169  |  |  |  |

| EPM5032                                 | 151      | PLDS2             | 171  |  |  |  |

| EPM5032-2                               | 151      | PLE3-12           | 221  |  |  |  |

| EPM5064                                 | 143      | PLE40             | 178  |  |  |  |

| EPM5127                                 | 150      | PLEJ1210          | 222  |  |  |  |

| EPM5128                                 | 150      | PLED1400          | 222  |  |  |  |

| EPS448-16                               | 105      | PLEJ1400          | 222  |  |  |  |

| EPS448-20                               | 105      | PLEG1800          | 222  |  |  |  |

| EPS448-25                               | 105      | PLEJ1800          |      |  |  |  |

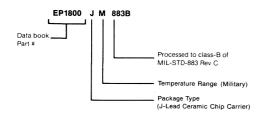

| EP1800                                  | 20       | PLEJ2001          | 222  |  |  |  |

| EP1800-2                                | 20       | PLED448           | 222  |  |  |  |

| EP1800-3                                | 20       | PLEJ448           |      |  |  |  |

| EP1810-45                               | 10       | PLED5032          |      |  |  |  |

| EP1810-55                               | 10       | PLEJ5032          |      |  |  |  |

| EP310                                   | 75       | PLED512           |      |  |  |  |

| EP310-2                                 | 75       | PLEJ512           |      |  |  |  |

| EP310-3                                 | 75       | PLEJ5128          |      |  |  |  |

| EP320                                   | 63       | PLEG5128          |      |  |  |  |

| EP320-1                                 | 63       | PLED600           |      |  |  |  |

| EP320-2                                 | 63       | PLEJ600           |      |  |  |  |

| EP512-25                                | 50       | PLED900           |      |  |  |  |

| EP512-30                                | 50       | PLEJ900           |      |  |  |  |

| EP512-35                                | 50<br>50 | PLFSIM            |      |  |  |  |

| EP600                                   | 46       | PLSLIB-TTL        |      |  |  |  |

| EP600-3                                 | 46       | PLS-MAX           |      |  |  |  |

| EP610-25                                | 37       | PLS-MCKIT         |      |  |  |  |

| EP610-25                                | 37       | PLS-SAM           | 211  |  |  |  |

| EP610-35                                | 37       | PLS2              |      |  |  |  |

|                                         | 37       |                   |      |  |  |  |

|                                         | 33       | PLSME<br>PLSTART  |      |  |  |  |

| ======================================= | 33       | PLOTART           | 210  |  |  |  |

|                                         | 33<br>33 |                   |      |  |  |  |

|                                         |          |                   |      |  |  |  |

| EP910-30                                | 24       |                   |      |  |  |  |

| EP910-35                                | 24       |                   |      |  |  |  |

| EP910-40                                | 24       |                   |      |  |  |  |

| EP910-45                                | 24       |                   |      |  |  |  |

### **ALTERA CORPORATION**

Altera Corporation was founded in 1983 to provide an alternative solution to custom masked gate arrays for the design of high-density logic functions. The founders of Altera believed that the problems of high development costs, long lead times, lack of design iteration flexibility and dedicated inventory could be eliminated through the use of standard, user configurable (or programmable) components.

### USER CONFIGURABLE

### INTEGRATED CIRCUITS

By combining CMOS and EPROM erasable cell technologies Altera created the industry's first Erasable Programmable Logic Device (EPLD). This led to the introduction of a full family of EPLDs spanning the range from 300 to over 2000 gates. These products provided a convenient, low cost means of integrating dozens of TTL and CMOS SSI/MSI devices into a handful of packages.

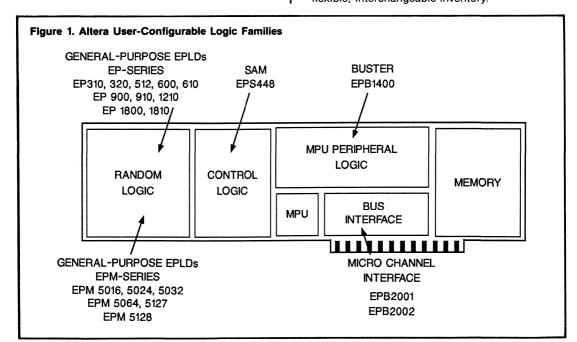

Today Altera offers EPLDs to solve many common board and system integration needs. These User Configurable logic devices are divided into two architectural categories based on a fundamental design decision—should the device architecture yield maximum flexibility for general purpose logic replacement or be specialized to solve a specific system design task:

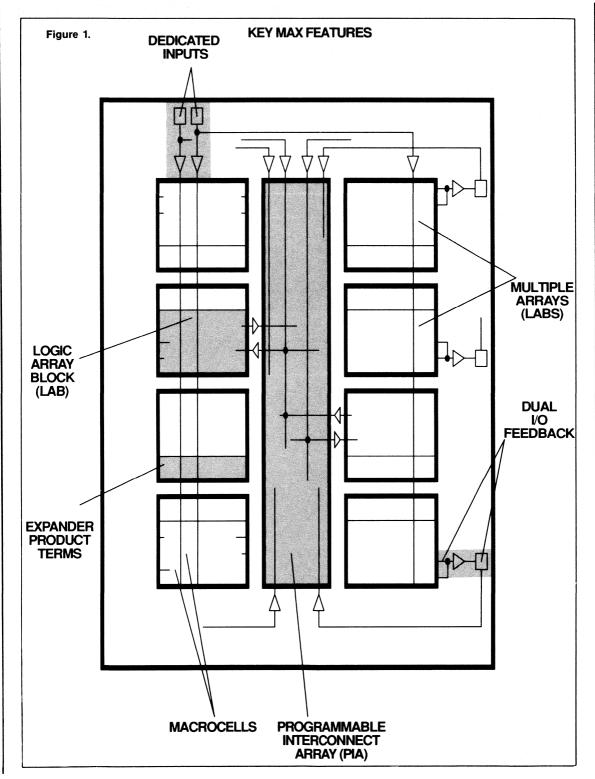

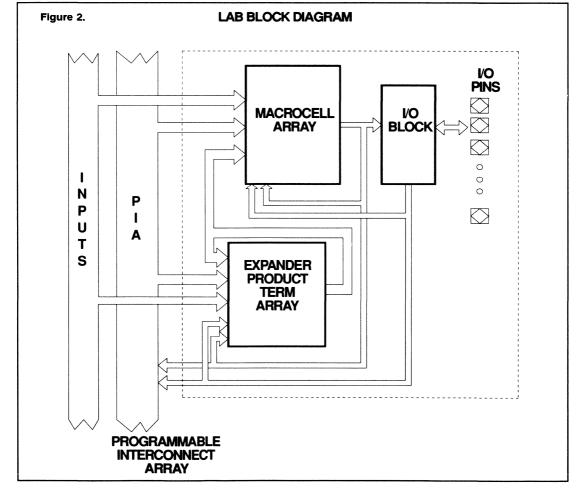

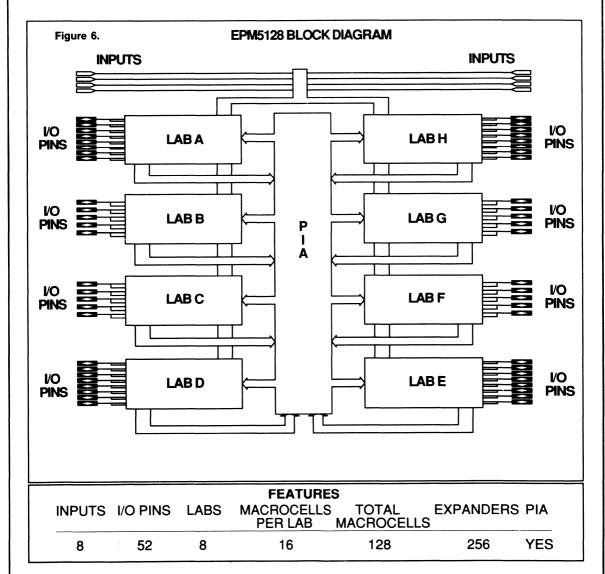

1) General Purpose EPLDs—provide ideal integration densities for random logic replacement from PAL replacement to thousands of gates. Two basic families of devices are available. The EP Series is based on a conventional AND-OR architecture. The EPM Series uses a Multiple Array matriX (MAX) structure for register intensive applications.

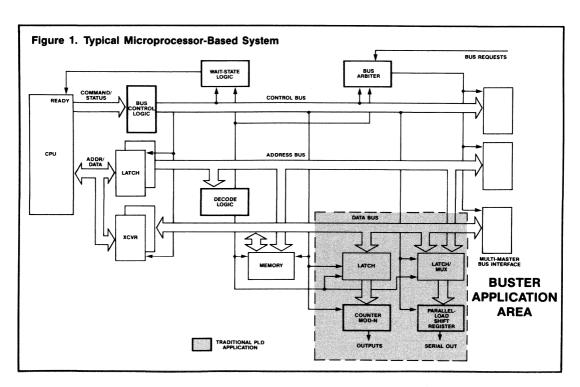

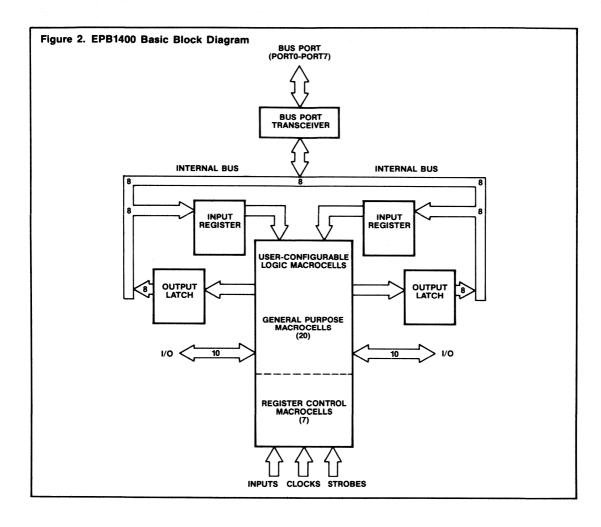

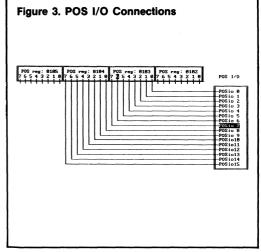

2) Function Specific EPLDs—provide integration of specific system design tasks. These function specific EPLDs are further divided into product families according to their specific system design focus: Families optimized for high performance controller/complex state machines, custom peripheral designs and Micro Channel interface applications are available today.

### **DEVELOPMENT TOOLS**

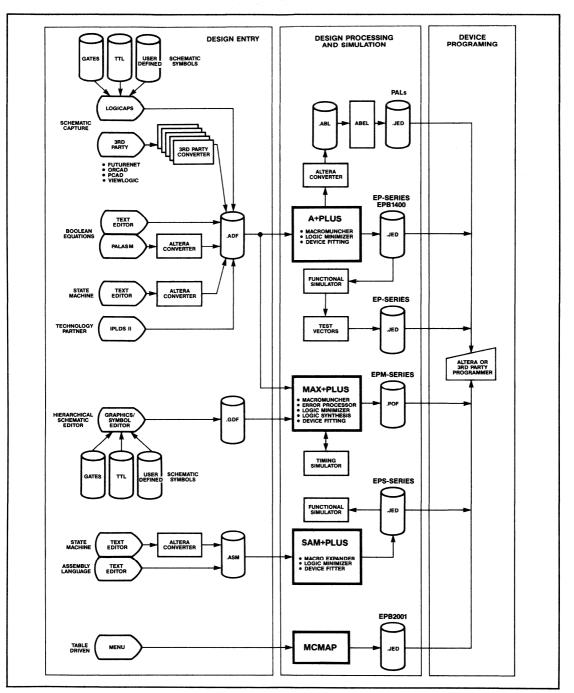

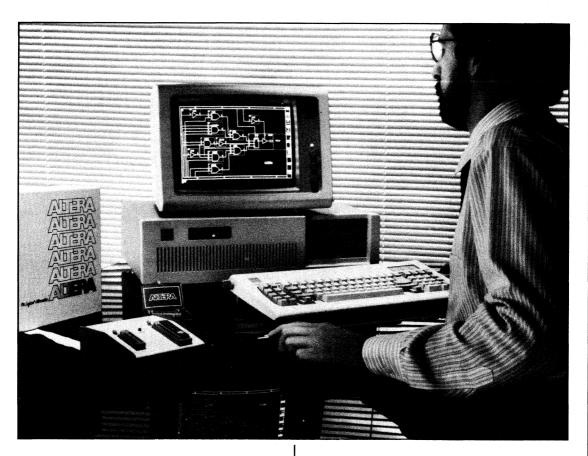

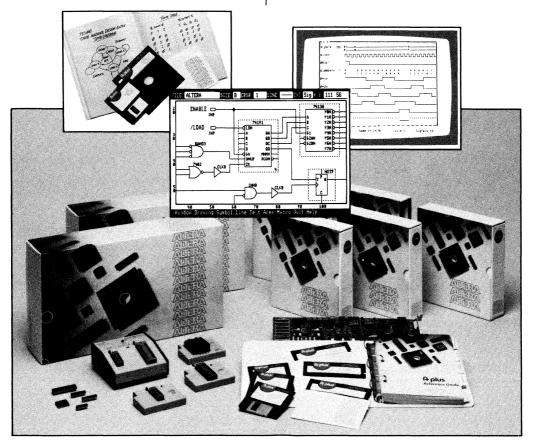

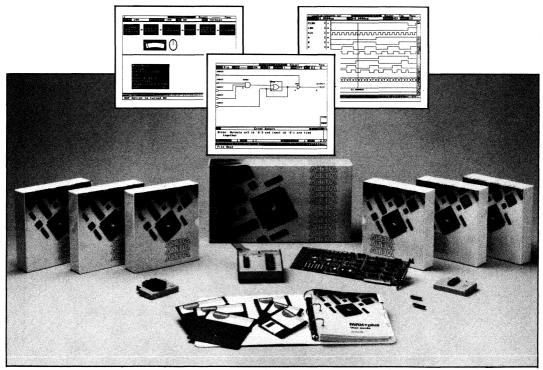

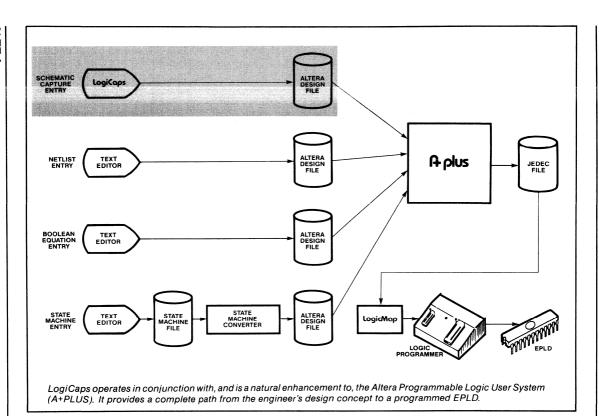

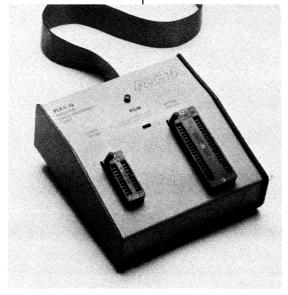

A critical factor in the rapid, worldwide acceptance of Altera's user configurable ICs has been the availability of low cost, easy to use software and hardware development tools. Available on both IBM PC compatible and PS/2 computer platforms, Altera's tools provide everything required to design, debug and program custom logic functions in the user's facility.

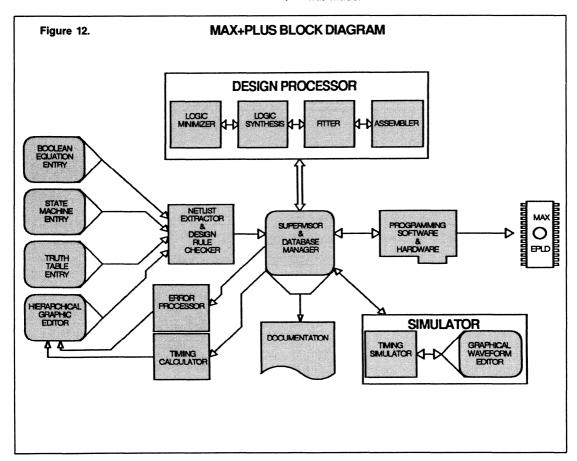

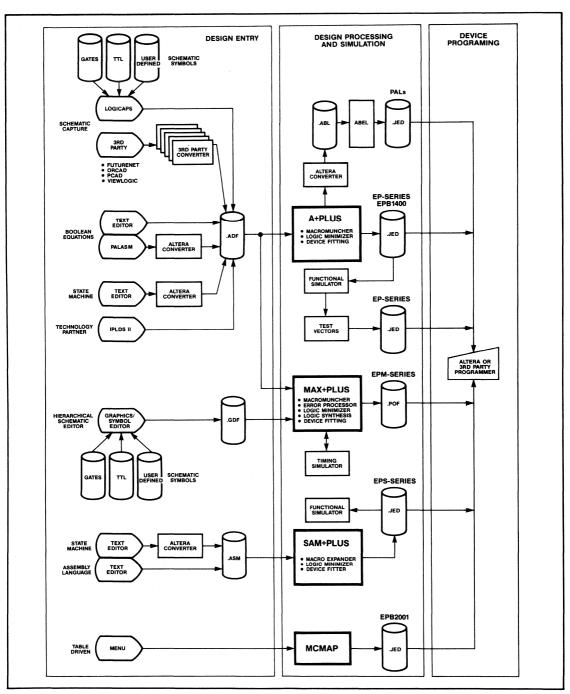

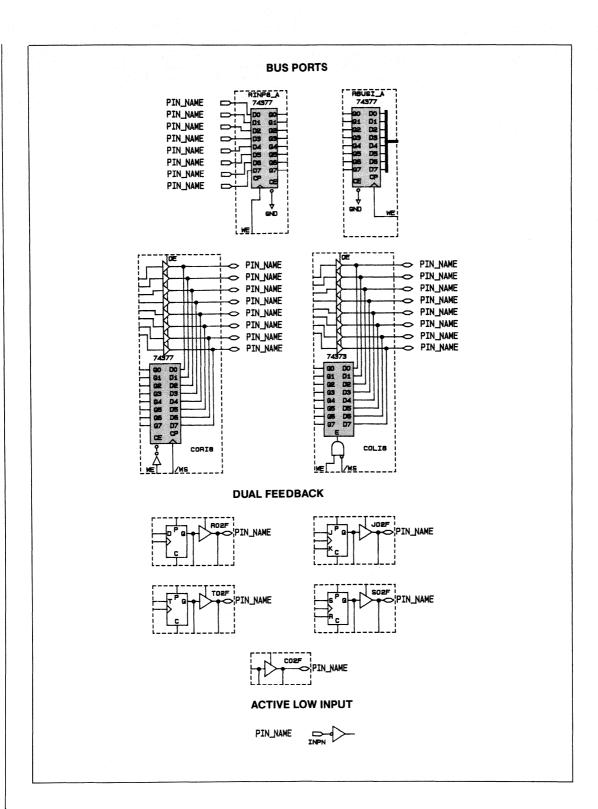

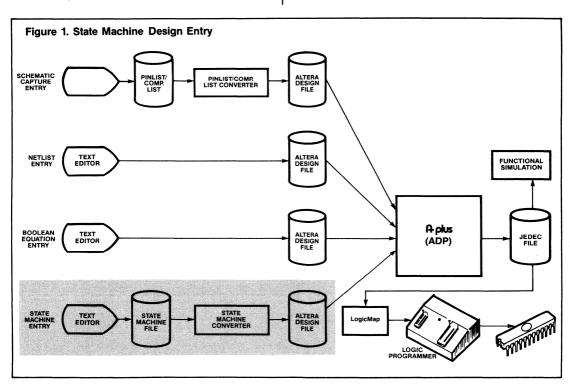

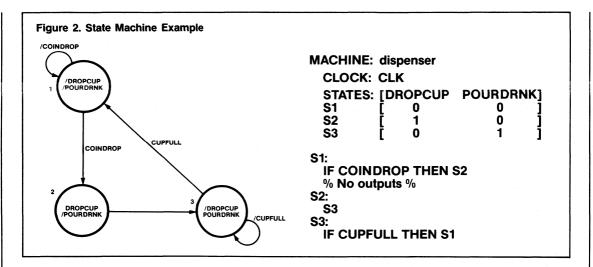

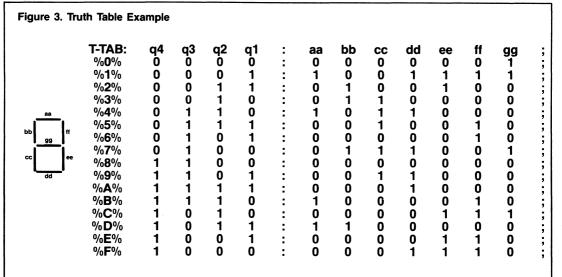

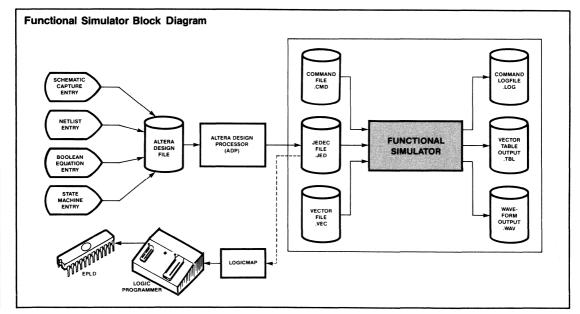

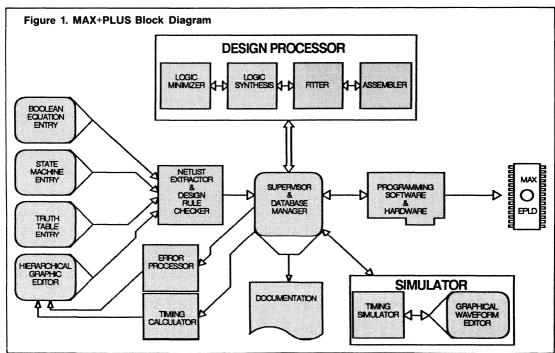

At the heart of these software tools are proprietary design processors based on logic synthesis techniques which automatically translate the user's input into programming patterns for the minimum device necessary to accomplish the task. A variety of design entry methods is offered including state machine and schematic capture using high level TTL MacroFunction building blocks as well as primitive gate elements. Simulation and interface programs to third party CAE products are also available.

The unique characteristic of EPLD technology is the very fast design turnaround times which can be achieved. Design processing is fast. A typical 1000 gate design will compile in less than 2 minutes and devices can be programmed in seconds. This, coupled with the erasable and reprogrammable features of an EPLD, allows multiple hardware iterations to be evaluated in a single day, if necessary.

#### PHILOSOPHY AND DIRECTION

Altera believes that these development tools are a critical factor for the advancement of user configurable semiconductor technology. In order that component utility and ultimately designer efficiency be maximized, the semiconductor device and the software must be developed in parallel and concert. If one is subordinated to the other, the total product combination will suffer. In line with this belief, Altera has invested in approximately equal sized R&D staffs in the areas of Software Development and Integrated Circuit Design.

One benefit of this approach is that when Altera introduces a new product to the market place, software and hardware support are in place on the day of introduction. This level of support and service is unique in the industry.

Altera also works closely with the leading third party vendors to assure its customers the availability of appropriate tools for the production environment.

Altera's products are sold by manufacturers representatives and major electronic distributors throughout the world. Cypress Semiconductor, Intel Corporation, Texas Instruments and others are licensed second sources for many of the Altera products described in this catalog.

### THE USER CONFIGURABLE

### INTEGRATED CIRCUIT CONCEPT

To achieve improved system performance in the marketplace, more and more manufacturers have sought higher levels of integration (functional density) for the electronic components in their products. This has led to various forms of custom chips that require lengthy development lead times and sizable design costs. The concept of User Configurable Integrated Circuits is to provide the benefits of large scale integration without the drawbacks of custom chips.

A few of the most significant benefits of large scale logic integration are:

- Lower manufacturing costs

- Lower power

- · Higher reliability

- · Proprietary design protection

- · Additional features

As end users of semiconductors moved to higher and higher levels of integration, chip designers found it increasingly difficult to define larger and larger common "building blocks" of logic. These difficulties led to the emergence of the user-defined Application-Specific Integrated Circuit (ASIC), sometimes more accurately described as the User Specific (USIC) or Customer Specific (CSIC) devices.

The options presently available for customerspecific logic are:

- Full Custom

- Standard Cell Library

- Gate Array

- User Configurable (Programmable)

The first three choices are custom masked and are not wholly satisfactory for system designers and manufacturers due to several problems:

- Development lead times are relatively long, requiring from 6 to 20 weeks for the fastest solution.

- Design costs are significant, varying from \$10K to \$40K as a minimum.

- Inventory is dedicated which is expensive and prohibits adequate second sourcing.

- Semiconductor distributors have difficulty participating in this business—thus limiting widespread use.

- None of these solutions address the fundamental issue that engineering is inherently an interactive process. Design changes in midstream are not allowed due to lead time and inventory constraints.

As a result of these restrictions, many designers are still reluctant to switch from standard logic to application-specific logic.

Attempts to eliminate these restrictions have led to an increasing interest in user configurable or programmable logic devices. The concept of user-configurable logic is to provide the designer with the benefits of custom LSI chips from standard products. The benefits of such parts include off-the-shelf availability, minimal design costs, multiple sourcing from distributors and manufacturers, and flexible, interchangeable inventory.

### **BIPOLAR FUSE TECHNOLOGY**

In the past all programmable logic products were implemented using bipolar fuse technology. These products eliminated the lead time and development cost penalties of the mask customized solution previously mentioned, but brought with them their own inherent limitations:

- Bipolar, with its high power dissipation, cannot provide the integration density required.

- Fuse programming does not allow complete testing at the factory and is inefficient in silicon utilization.

- The devices can only be programmed once; therefore, mistakes in development result in scrap, a significant penalty with high density parts.

- The programming software and development tools are primitive and tedious to use.

### **CMOS ERASABLE TECHNOLOGY**

Altera was the first supplier to overcome these problems of programmable logic when it introduced its EPLD line of user-programmable logic devices incorporating CMOS floating-gate technology.

Altera EPLDs are manufactured with high-speed complementary metal oxide semiconductor (CMOS) technology. Compared to bipolar fuse technology, CMOS provides lower power dissipation and a cooler operating temperature which enables designers to pack a greater number of logic functions onto a chip.

Altera's EPLDs use an EPROM programming mechanism. This technology, used in MOS memories since the early 1970s, brings further advantages. It enables the devices to be reprogrammed in the event of any design changes. The fact that programming can be erased also permits thorough testing during the manufacturing process.

### **EASY TO USE DESIGN TOOLS**

For user-configurable circuits to reach the broad base of existing SSI/MSI TTL users, the programming and design tools must meet three criteria:

- Low cost

- · Easy to use

- Personal availability and access.

Today, the most widely available source of computing power is the personal computer. By creating development tools that fit the personal computer environment, all three of these criteria can be met.

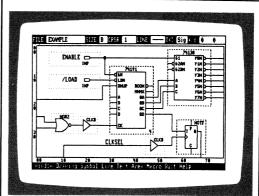

As in the area of component architecture, Altera is committed to provide effective, flexible solutions to the CAD/CAE problems the system designer faces. Particularly in those areas which require extensive device-specific knowledge, Altera has developed an effective set of IBM-PC and PS/2

based CAE tools to handle the problems of design entry and programming.

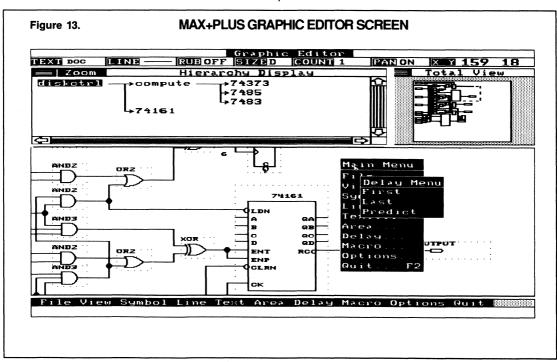

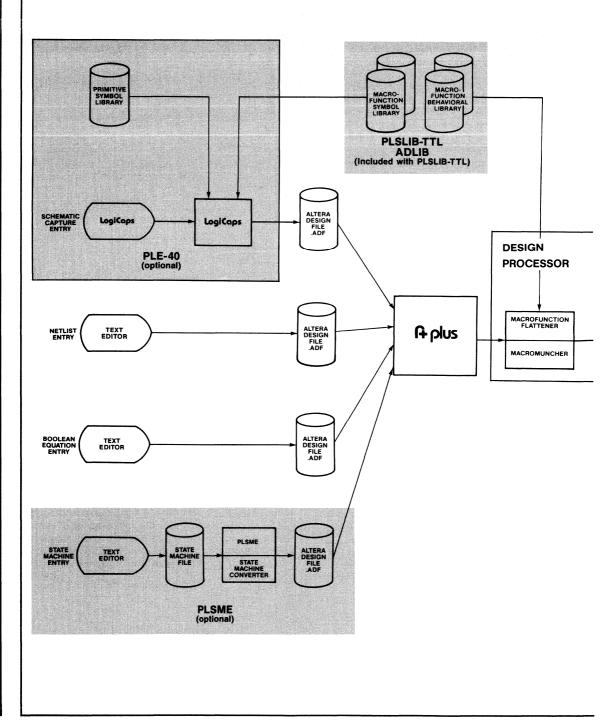

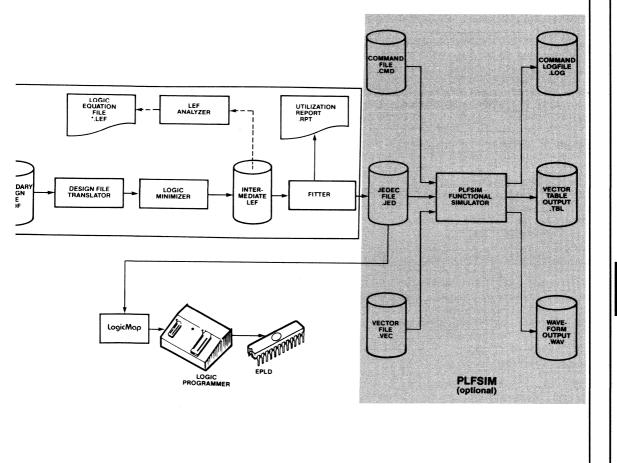

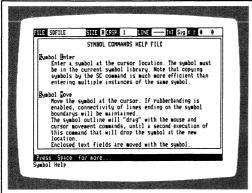

With these tools the user may enter a design via high level TTL MacroFunctions or primitive gate symbols using graphic schematic diagrams, text based netlist entries, state machine descriptions, or Boolean equations. Once the design is entered, a fully automated integration process, called the Design Processor, translates the design into a device programming file. This file is used to directly program the target EPLD using Altera-supplied hardware, or general-purpose third party programmers.

### LOGIC SYNTHESIS

The translation of a design from its original input format (be it equation, schematic, or other) to a device-specific programming map is typically called logic synthesis. Early PAL device assemblers provided no support for software-assisted logic minimization: the user in essence had to determine the minimal set of equations to implement his logic. This could be quite time-consuming and was recognized as a mechanical task well suited to software algorithms.

Altera's design processors, such as A+PLUS, SAM+PLUS and MAX+PLUS, use logic minimization schemes such as DeMorgan's Inversion to aid the designer in minimizing his logic and optimally fitting into a given device. This process become more complex as devices become more sophisticated. Variable product term distribution, multiple flip-flop types, local/global feedback all complicate the process as they add capability.

The appropriate algorithm for fitting a large design into an EPLD is a process which is sensitive to device architecture. A compelling reason for vendor-supplied development tools is the need for close interaction between tools and architecture. Much as optimizing compilers must have knowledge of the target computer architecture, logic synthesizers must have knowledge of their devices. Tools developed in parallel with device development will arrive in a timely fashion at device introduction rather than lagging by substantial periods of time.

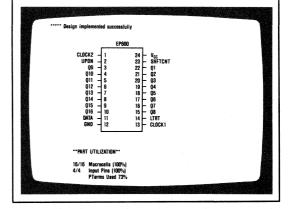

Altera's synthesis package for general purpose EPLDs is the A+PLUS package. It performs three major functions.

First, regardless of the type of design entry method used, it translates the design into internal logic equations. At this stage, most design syntax errors are detected and reported to the user.

Second, it performs sophisticated Boolean logic reductions on the translated design in order to maximize utilization of the EPLD's resources. The user is given complete control over the application of minimization and inversion techniques.

Finally, A+PLUS matches requirements of a specific design with the known resources of an Altera part. Automatically, or with user input, each logic function is placed in the optimum location

and selects the appropriate interconnection paths and device pin assignments.

The actual fitting process results in a utilization report and a programming file. The utilization report informs the user how the design was implemented and points out any unused resources remaining in the device.

### SIMULATION AND

### **TEST CONSIDERATIONS**

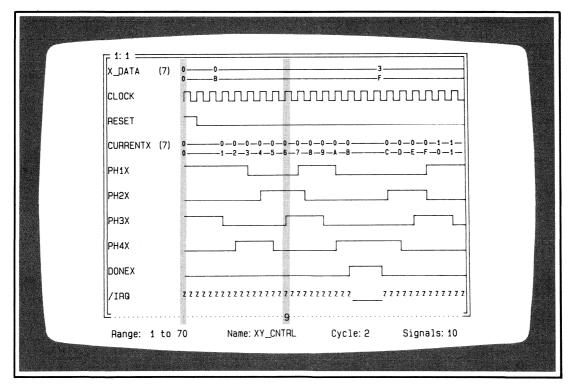

Design checking before system integration from components has taken on new importance with more complex designs. Granted, with EPLDs the user does have the luxury of relatively painlessly reprogramming his device if an error in the design should be found. However, by employing simulation at an early stage this type of wasted effort can be prevented. Altera offers P.C. based simulation capability.

Most customer specific logic solutions, such as gate arrays and the fuse based PLDs, required extensive customer investment in test program development and test equipment. EPLDs eliminate this need to develop specific tests for the unique design programmed into each device. Because it is erasable, each cell can be programmed and tested prior to shipment from the factory. Through this generic testability the I/C manufacturer can guarantee 100% programming yield to their user.

### SUMMARY

Altera, with its EPLD products and development system support tools, has addressed the limitations of gate arrays and fuse programmable logic. The benefits to the system designer are:

- · no lead times

- low design costs

- multiple sourcing from distributors and manufacturers

- · ease of design changes

- · low power dissipation from CMOS technology

- high density products that maximize function, integration, and quality

- maximum flexibility in each chip that comes from programmable architecture, and the ability to erase and reprogram

- a self-contained low-cost sophisticated development system.

EPLDs are now a cost-effective solution to the problem of large scale random logic integration. EPLDs are the simplest form of high-density application-specific logic to implement. As such, they will be a key ingredient to boosting electronic engineering productivity over the next decade.

### **DEVICE SELECTOR GUIDE**

### **General Purpose EPLDs EP-Series**

| EPLD                                 | PACKAGE                           | PINS                 | MACROCELLS<br>(REGISTERS) | BURIED<br>REGISTERS | INPUTS               | 1/0                  | Fmax MHz                     | lcc mA                       | STANDBY<br>ICC ma        |

|--------------------------------------|-----------------------------------|----------------------|---------------------------|---------------------|----------------------|----------------------|------------------------------|------------------------------|--------------------------|

| EP1810J                              | JLCC                              | 68                   | 48                        | 16                  | 16                   | 48                   | 33.3                         | 45.0                         | 0.15                     |

| EP1810L                              | PLCC                              | 68                   | 48                        | 16                  | 16                   | 48                   | 33.3                         | 45.0                         | 0.15                     |

| EP1810G                              | PGA                               | 68                   | 48                        | 16                  | 16                   | 48                   | 33.3                         | 45.0                         | 0.15                     |

| EP1800J                              | JLCC                              | 68                   | 48                        | 16                  | 16                   | 48                   | 20.8                         | 30.0                         | 0.15                     |

| EP1800L                              | PLCC                              | 68                   | 48                        | 16                  | 16                   | 48                   | 20.8                         | 30.0                         | 0.15                     |

| EP1800G                              | PGA                               | 68                   | 48                        | 16                  | 16                   | 48                   | 20.8                         | 30.0                         | 0.15                     |

| EP910D<br>EP910P<br>EP910J<br>EP910L | CerDIP<br>OTP DIP<br>JLCC<br>PLCC | 40<br>40<br>44<br>44 | 24<br>24<br>24<br>24      | _<br>_<br>_         | 12<br>12<br>12<br>12 | 24<br>24<br>24<br>24 | 41.7<br>41.7<br>41.7<br>41.7 | 20.0<br>20.0<br>20.0<br>20.0 | 0.1<br>0.1<br>0.1<br>0.1 |

| EP900D                               | CerDIP                            | 40                   | 24                        |                     | 12                   | 24                   | 26.3                         | 15.0                         | 0.15                     |

| EP900P                               | OTP DIP                           | 40                   | 24                        |                     | 12                   | 24                   | 26.3                         | 15.0                         | 0.15                     |

| EP900J                               | JLCC                              | 44                   | 24                        |                     | 12                   | 24                   | 26.3                         | 15.0                         | 0.15                     |

| EP900L                               | PLCC                              | 44                   | 24                        |                     | 12                   | 24                   | 26.3                         | 15.0                         | 0.15                     |

| EP610D                               | CerDIP                            | 24                   | 16                        |                     | 4                    | 16                   | 47.6                         | 10.0                         | 0.1                      |

| EP610P                               | OTP DIP                           | 24                   | 16                        |                     | 4                    | 16                   | 47.6                         | 10.0                         | 0.1                      |

| EP610J                               | JLCC                              | 28                   | 16                        |                     | 4                    | 16                   | 47.6                         | 10.0                         | 0.1                      |

| EP610L                               | PLCC                              | 28                   | 16                        |                     | 4                    | 16                   | 47.6                         | 10.0                         | 0.1                      |

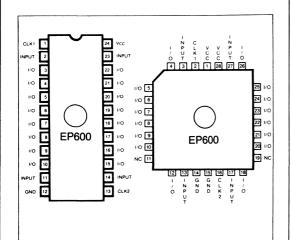

| EP600D                               | CerDIP                            | 24                   | 16                        |                     | 4                    | 16                   | 26.3                         | 10.0                         | 0.15                     |

| EP600P                               | OTP DIP                           | 24                   | 16                        |                     | 4                    | 16                   | 26.3                         | 10.0                         | 0.15                     |

| EP600J                               | JLCC                              | 28                   | 16                        |                     | 4                    | 16                   | 26.3                         | 10.0                         | 0.15                     |

| EP600L                               | PLCC                              | 28                   | 16                        |                     | 4                    | 16                   | 26.3                         | 10.0                         | 0.15                     |

| EP512D                               | CerDIP                            | 24                   | 12                        | _                   | 10                   | 12                   | 50.0                         | 50.0                         | 0.15                     |

| EP512P                               | OTP DIP                           | 24                   | 12                        | _                   | 10                   | 12                   | 50.0                         | 50.0                         | 0.15                     |

| EP512J                               | JLCC                              | 28                   | 12                        | _                   | 10                   | 12                   | 50.0                         | 50.0                         | 0.15                     |

| EP512L                               | PLCC                              | 28                   | 12                        | _                   | 10                   | 12                   | 50.0                         | 50.0                         | 0.15                     |

| EP320D                               | CerDIP                            | 20                   | 8                         |                     | 10                   | 8                    | 45.5                         | 5.0                          | 0.15                     |

| EP320P                               | OTP CIP                           | 20                   | 8                         |                     | 10                   | 8                    | 45.5                         | 5.0                          | 0.15                     |

| EP310D                               | CerDIP                            | 20                   | 8                         |                     | 10                   | 8                    | 35.7                         | 40.0                         | 0.15                     |

|                                      |                                   |                      | MACRO CELLS               | BURIED              |                      |                      |                              |                              | STANDBY                  |

### **EPM-Series**

|   | EPLD    | PACKAGE   | PINS  | (REGISTERS) | REGISTERS | INPUTS | 1/0 |              | cc mA |

|---|---------|-----------|-------|-------------|-----------|--------|-----|--------------|-------|

| Γ | EPM5016 | DIP       | 20    | 16          | 8         | 8      | 8   | TBA          |       |

|   | EPM5024 | DIP/JLead | 24/28 | 24          | 12        | 8      | 12  | TBA          |       |

|   | EPM5032 | DIP/JLead | 28/28 | 32          | 16        | 8      | 16  | 83.3 200.0 1 | 0.001 |

|   | EPM5064 | DIP/JLead | 40/44 | 64          | 36        | 8      | 28  | TBA          |       |

| 1 | EPM5127 | DIP/JLead | 40/44 | 128         | 100       | 8      | 28  | TBA          |       |

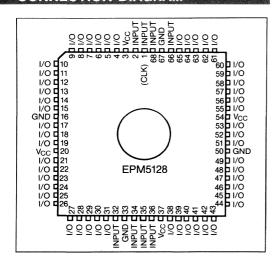

|   | EPM5128 | JLead/PGA | 68/68 | 128         | 76        | 8      | 52  | TBA          |       |

### **BUSTER Custom** Peripheral EPLDs

| EPLD     | PACKAGE | PINS | MACROCELLS<br>(REGISTERS) | I/O<br>Registers | INPUTS | 1/0 | Fmax MHz | lcc mA | STANDBY<br>Icc mA |

|----------|---------|------|---------------------------|------------------|--------|-----|----------|--------|-------------------|

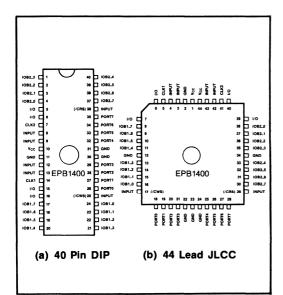

| EPB1400D | CerDIP  | 40   | 20                        | 32               | 8      | 28  | 40.0     | 100.0  | 100.0             |

| EPB1400P | OTP DIP | 40   | 20                        | 32               | 8      | 28  | 40.0     | 100.0  | 100.0             |

| EPB1400J | JLCC    | 40   | 20                        | 32               | 8      | 28  | 40.0     | 100.0  | 100.0             |

| EPB1400L | PLCC    | 40   | 20                        | 32               | 8      | 28  | 40.0     | 100.0  | 100.0             |

### **SAM Stand-Alone** Microsequencer **EPLDs**

| EPLO    | PACKAGE | PINS | MICROCODE<br>Eprom | BRANCH<br>EPLD | INPUTS | 1/0 | Fmax MHz | lcc mA | STANDBY<br>ICC mA |

|---------|---------|------|--------------------|----------------|--------|-----|----------|--------|-------------------|

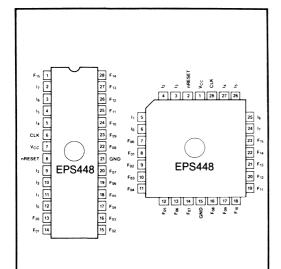

| EPS448D | CerDIP  | 28   | 448x36             | 768 P-Term     | 8      | 16  | 25.0     | 120.0  | 65.0              |

| EPS448P | OTP DIP | 28   | 448x36             | 768 P-Term     | 8      | 16  | 25.0     | 120.0  | 65.0              |

| EPS448J | JLCC    | 28   | 448x36             | 768 P-Term     | 8      | 16  | 25.0     | 120.0  | 65.0              |

| EPS448L | PLCC    | 28   | 448x36             | 768 P-Term     | 8      | 16  | 25.0     | 120.0  | 65.0              |

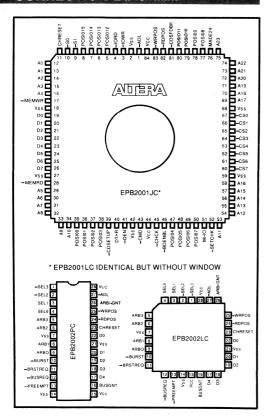

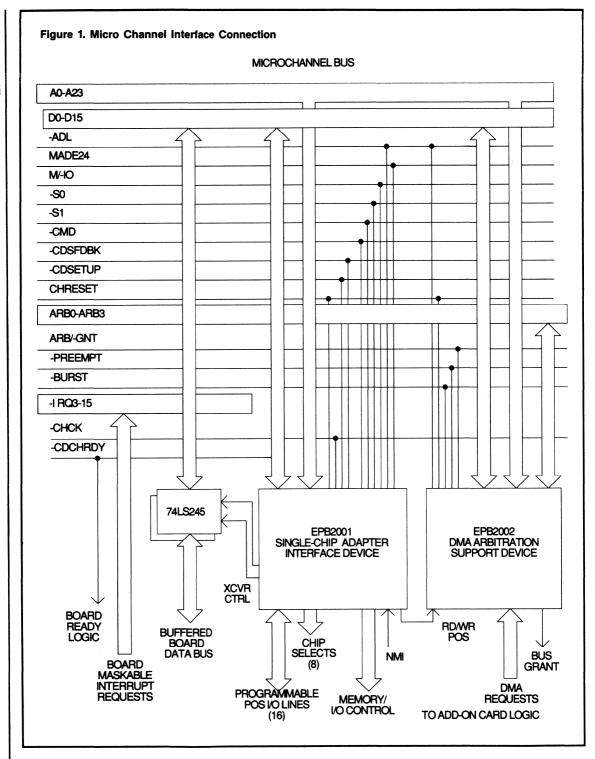

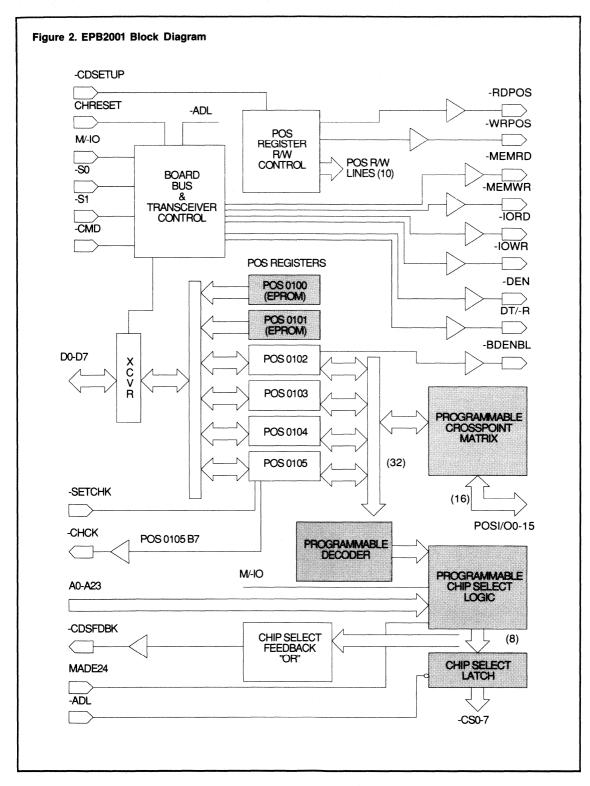

### Interface Integration **EPLDs**

| EPB2001 | JLCC   | 84 | SINGLE CHIP, MICROCHANNEL ADAPTOR INTERFACE |  |

|---------|--------|----|---------------------------------------------|--|

| EPB2001 | PLCC   | 84 |                                             |  |

| EPB2002 | CerDIP | 28 | DMA ARBITRATION SUPPORT DEVICE              |  |

| EPB2002 | JLCC   | 28 |                                             |  |

| EPB2002 | PLCC   | 28 |                                             |  |

#### Package Abbreviations:

CEPDIP = windowed ceramic dual-in-line.

OTP DIP = one-time-programmable plastic dual-in-line.

JLCC = windowed ceramic leaded chip-carrier.

PGA = windowed ceramic pin-grid array.

| DEVICE DATASHEETS           | PAGE NO. |

|-----------------------------|----------|

| EP1810                      | 10       |

| EP1800                      | 20       |

| EP910                       |          |

| EP900                       |          |

| EP610                       |          |

| EP600                       |          |

| EP512                       |          |

| EP320                       |          |

| EP310                       | 75       |

| EPB1400 (BUSTER)            | 81       |

| EPS448 (SAM)                |          |

| EPB2001                     |          |

| EPB2002                     |          |

| Multiple Array MatriX (MAX) |          |

| Family Overview             | 136      |

| EPM5128                     |          |

| EPM5127                     |          |

| EPM5032                     | 151      |

| Design Recommendations      |          |

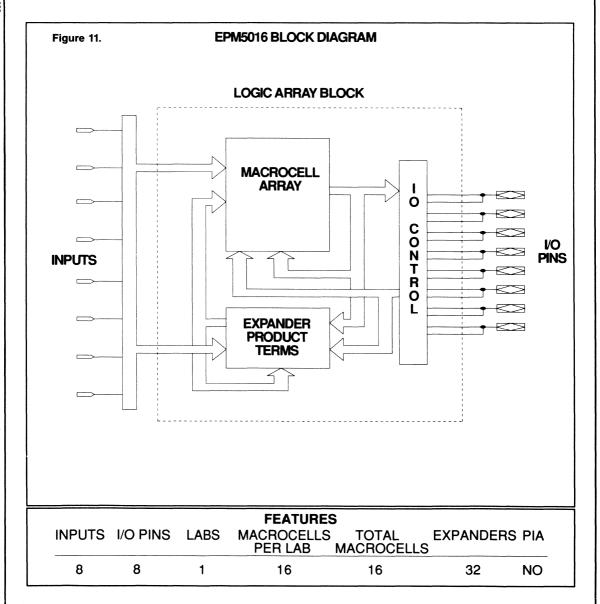

### **FEATURES**

- Erasable, User-Configurable LSI circuit capable of implementing 2100 equivalent gates of conventional and custom logic.

- Speed equivalent to 74LS TTL with 33 MHz clock rates.

- "Zero Power" (typically 35 μA standby).

- Active power of 250 mW at 5 MHz.

- Forty-eight Macrocells with configurable I/O architecture allowing 64 inputs or 48 outputs.

- Programmable clock option allows independent clocking of all registers.

- Accepts popular TTL SSI and MSI based Macro-Function design inputs.

- TTL/CMOS I/O compatibility.

- 100% generically testable—provides 100% programming yield.

- Full military capability.

- CAD support from Altera's A+PLUS Development System featuring schematic capture design entry with extensive Primitive and MacroFunction libraries.

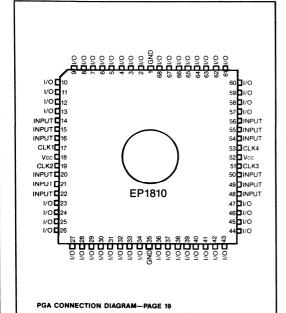

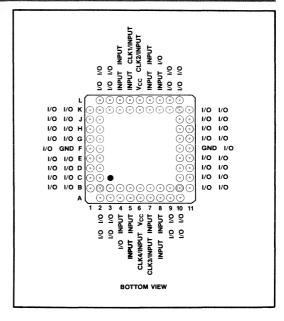

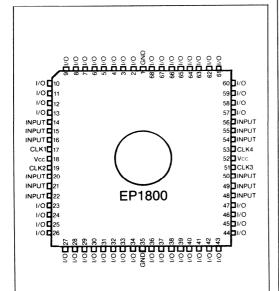

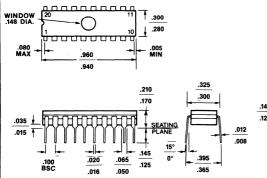

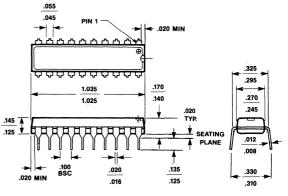

- Packaged in a 68 pin ceramic (window) and plastic (one-time programmable) JLCC, PLCC, and PGA configurations.

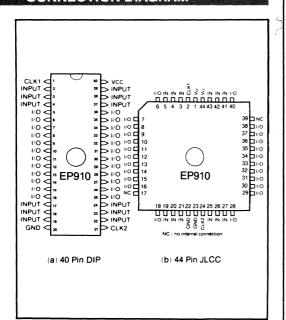

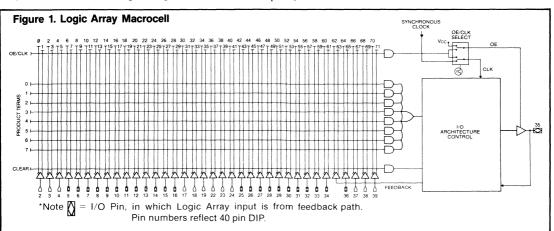

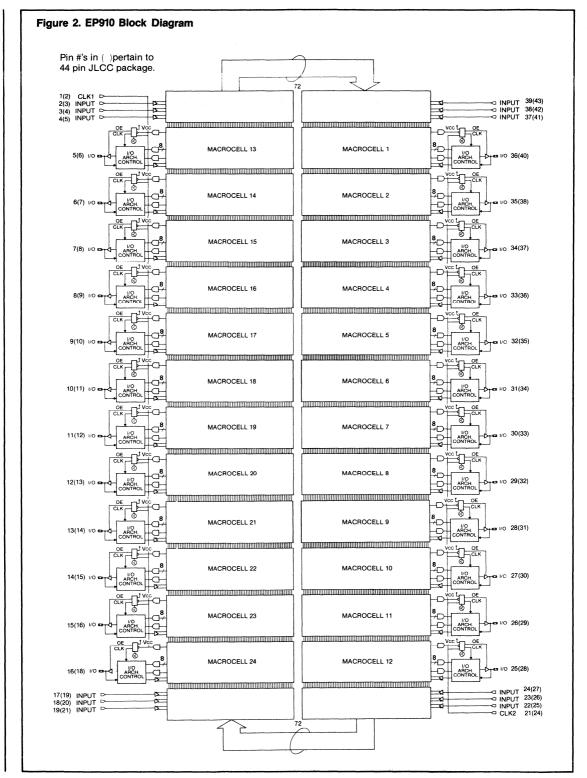

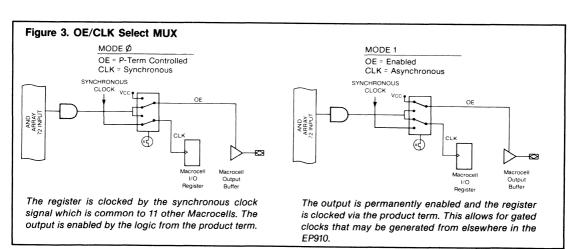

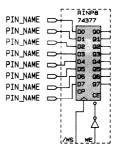

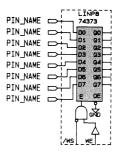

### **CONNECTION DIAGRAM**

### **GENERAL DESCRIPTION**

The EP1810 series of CMOS EPLDs from Altera offer LSI density, TTL equivalent speed performance and low power consumption. Each device is capable of implementing over 2100 equivalent gates of SSI, MSI and custom logic circuits. The EP1810 series is packaged a 68 pin J-Leaded Chip Carrier and Pin Grid Array, available in ceramic (erasable) and plastic (one-time-programmable) versions.

The EP1810 series is designed as an LSI replacement for traditional Low Power Schottky TTL logic circuits. Its speed and density also make it suitable for high performance complex functions such as dedicated peripheral controllers and intelligent support chips. IC count and power requirements can be reduced by several orders of magnitude allowing similar reduction in total size and cost of the system, with significantly enhanced reliability.

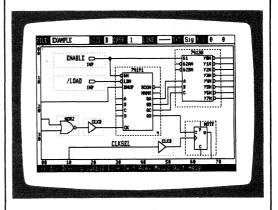

The EP1810 architecture has been configured to facilitate design with conventional TTL SSI and MSI building blocks as well as simple, optimized gate and flip-flop elements. Schematic descriptions of these functions are stored in a library. The desired TTL logic functions are selected and interconnected "on-screen" with a low cost, personal computer based, workstation. The Design Processor within Altera's A+PLUS Development System then automatically places the functions in appropriate locations within the EPLD's internal structure. Also included in the Development System is EPLD programming hardware and software. A+PLUS is available for the IBM Personal Computer (and compatibles).

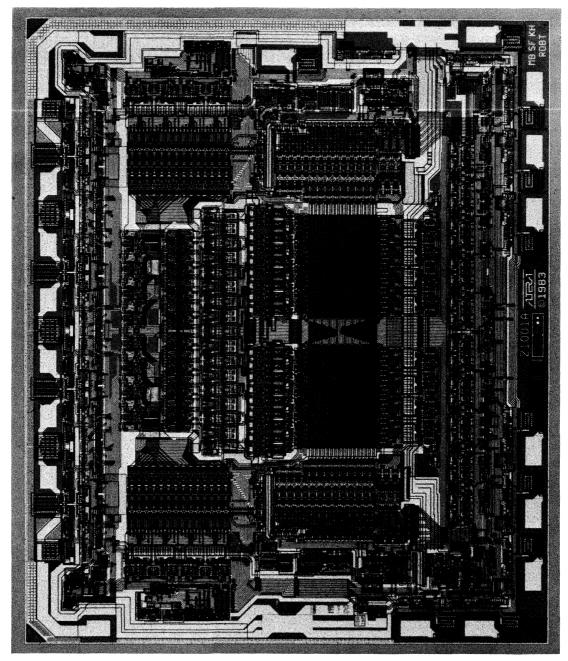

The EP1810 uses a 1.2 micron CMOS EPROM technology employing EPROM transistors to configure logic connections. User defined logic functions are constructed by selectively programming EPROM cells within the device. The EPROM technology also allows 100% generic testing (all devices are 100% tested at the factory). The devices can be erased with ultraviolet light. Design changes are no longer costly or time consuming, nor is there the need for post-programming testing.

#### PRELIMINARY DATA

NOTICE: THIS IS NOT A FINAL SPECIFICATION. SOME PARAMETRIC LIMITS ARE SUBJECT TO CHANGE.

**REV. 2.0**

#### **FUNCTIONAL DESCRIPTION**

The EP1810 series of Erasable Programmable Logic Devices (EPLDs) use CMOS EPROM cells to configure logic functions within the device. The EP1810 architecture is 100% user configurable, allowing the device to accommodate a variety of independent logic functions.

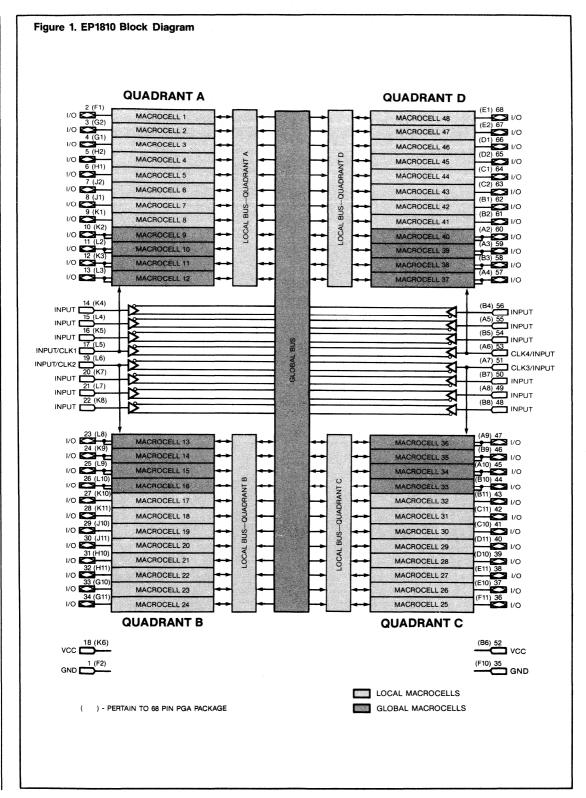

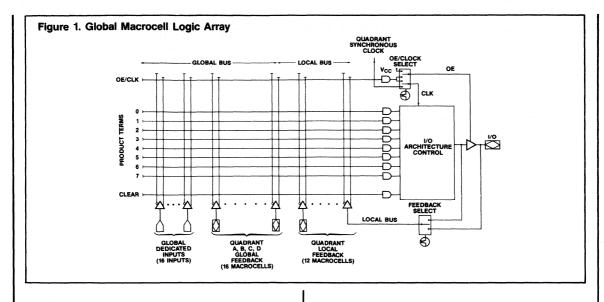

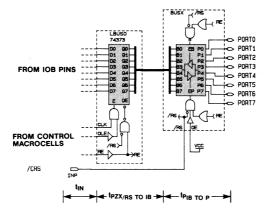

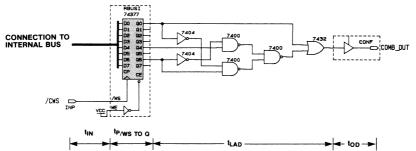

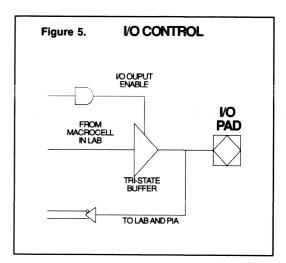

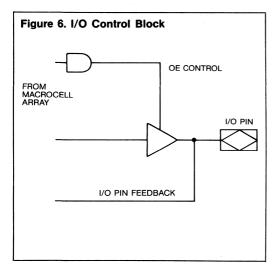

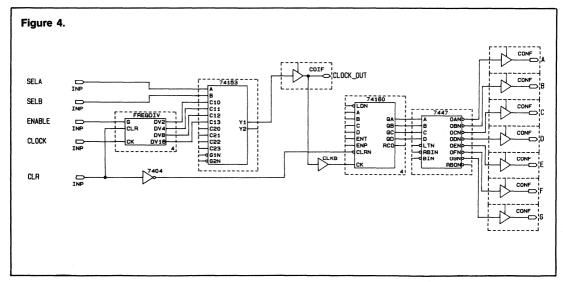

The Block Diagram is shown in Fig. 1. Externally, the EP1810 provides 16 dedicated data inputs, 4 of which may be used as system clock inputs. There are 48 I/O pins which may be individually configured for input, output, or bi-directional data flow.

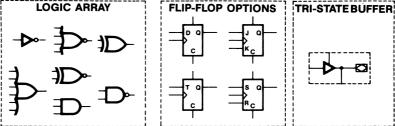

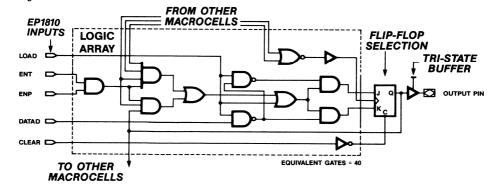

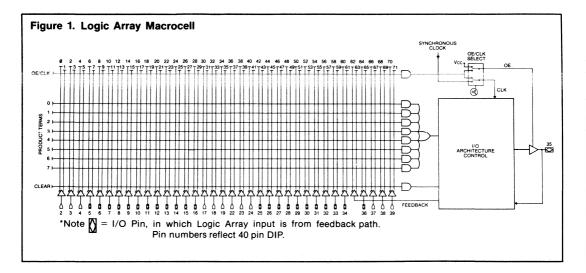

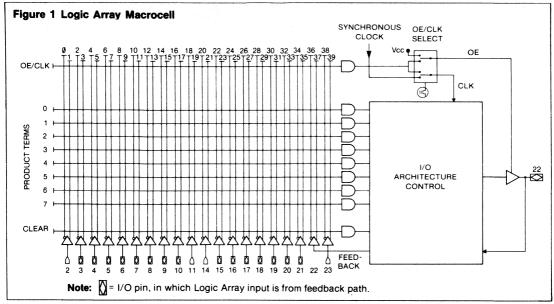

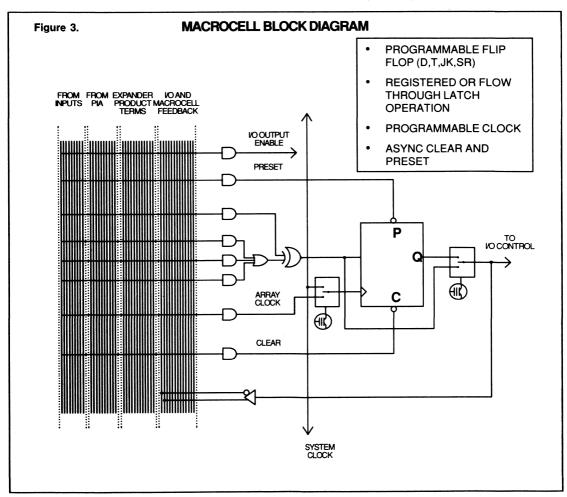

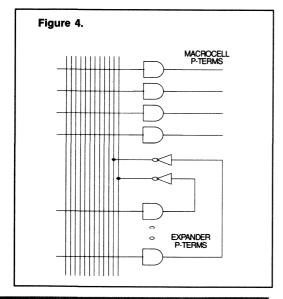

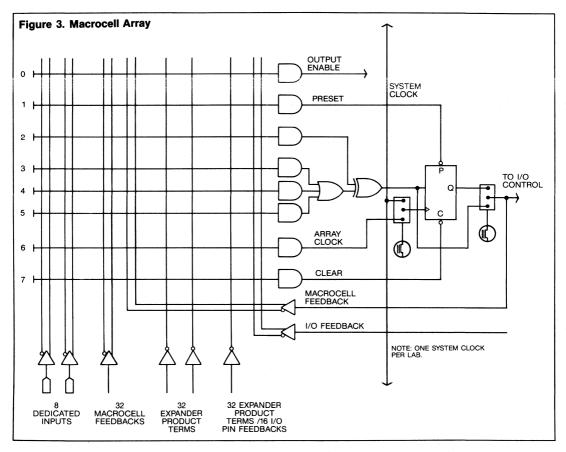

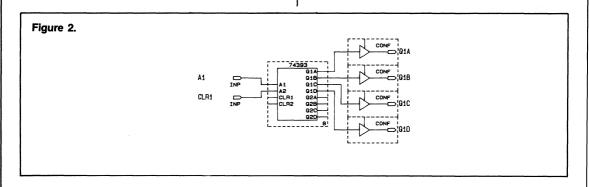

### **MACROCELLS**

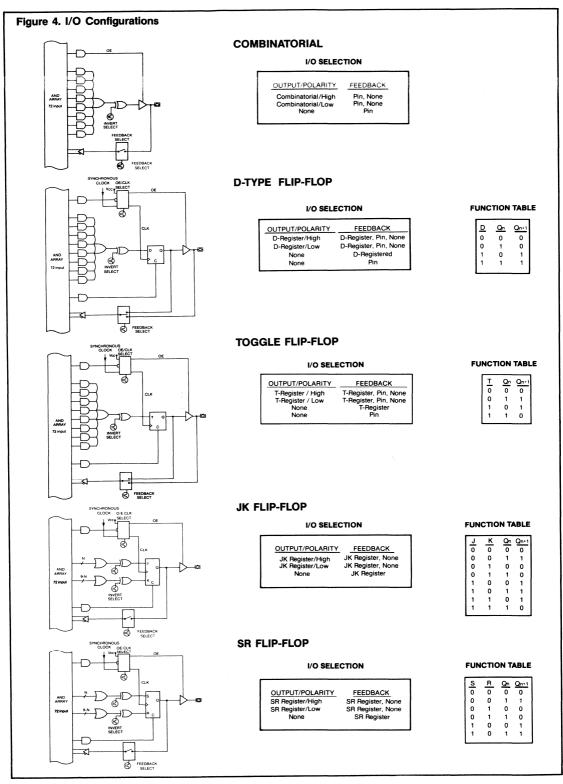

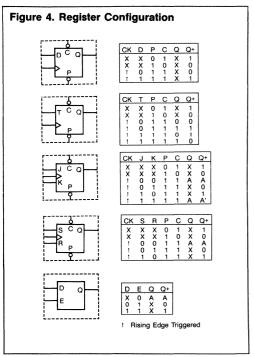

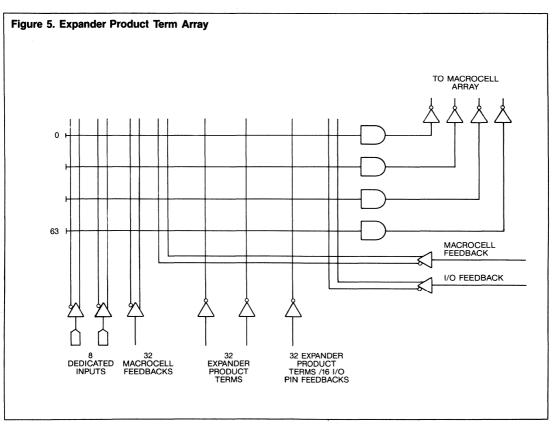

Internally, the EP1810 architecture consists of a series of Macrocells. All logic is implemented within these cells. Each Macrocell, shown in Fig. 2A, contains three basic elements: a Logic Array, a selectable register element, and a tri-state I/O buffer. All combinatorial logic such as Exclusive-OR, NAND, NOR, AND, OR and Invert gates are implemented within the Logic Array. For register applications each Macrocell provides one of 4 possible flip-flop options; D, T, JK, SR. Each EP1810 Macrocell is equivalent to over 40 2-input NAND gates.

The EP1810 is partitioned into four identical quadrants. Each quadrant contains 12 Macrocells. Input signals into the Macrocells come from the EP1810 internal bus structures. Macrocell outputs may drive the EP1810 external pins as well as the internal buses. Fig. 2B illustrates a simple logic function that can be implemented within a single Macrocell. Note that all combinatorial logic is implemented within the Logic Array, a JK flip-flop is selected, and the tri-state buffer is permanently enabled.

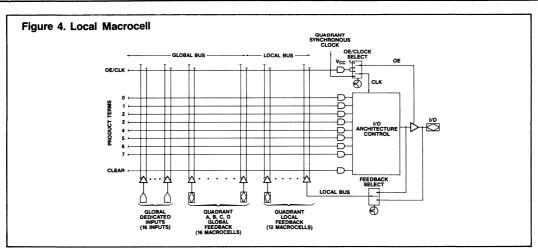

The EP1810 macrocell architecture is shown in Figures 4 and 5. Thirty two macrocells are "Local Macrocells." These Macrocells offer a multiplexed feedback path (pin or internal) which drives the Local Bus of the respective quadrant.

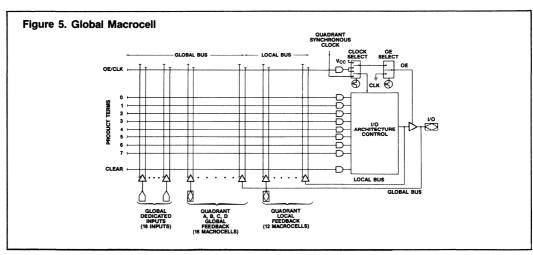

Another 16 Macrocells provide dual functions. These "Global Macrocells", see Figure 5, allow the Macrocell to implement buried logic functions and, at the same time, serve as dedicated input pins. Thus, the EP1810 may have an additional 16 input pins giving a total of 32 inputs. The global Macrocells have the same timing characteristics as the Local Macrocells.

### Figure 2A. Macrocell Components

Each 1810 Macrocell consists of 3 basic components:

(1) A logic array for gated logic. (2) a flip-flop for data storage (selectable options include D, T, JK, SR). The flip-flop may be bypassed for purely combinatorial functions. (3) A tri-state I/O buffer to define input, output or bi-directional data flow.

Figure 2B. Sample Circuit

Typical logic functional implemented into a single Macrocell. Each EP1810 Macrocell can accommodate the equivalent of 40 gates.

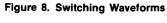

### **CLOCK OPTIONS**

Each of the EP1810 internal flip-flops may be clocked independently or in user defined groups. Any input or internal logic function may be used as a clock. These clock signals are activated by driving the flip-flop clock input with a clock buffer (CLKB) primitive. In this mode, the flip-flops can be configured for positive or negative edge triggered operation.

Four dedicated system clocks (CLK1-CLK4) also provide clock signals to the flip-flops. System clocks are connected directly from the EP1810 external pins. With this direct connection, system clocks give enhanced clock to output delay times than internally generated clock signals. There is one system clock per EP1810 quadrant. When using system clocks, the flip-flops are positive edge triggered (data transitions occur on the rising edge of the clock).

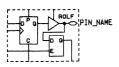

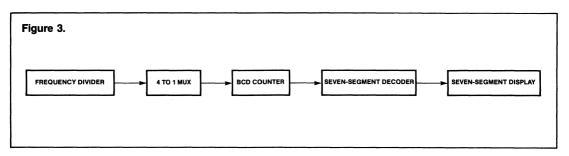

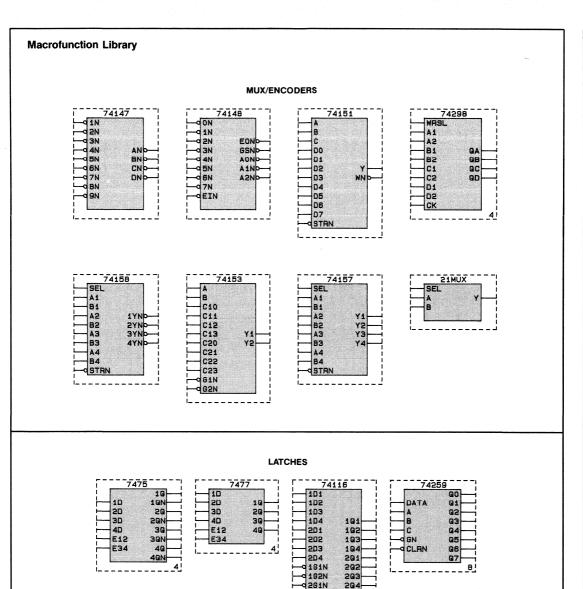

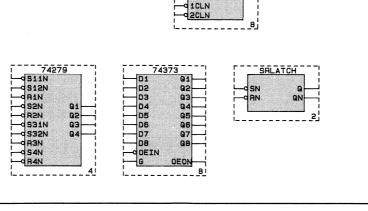

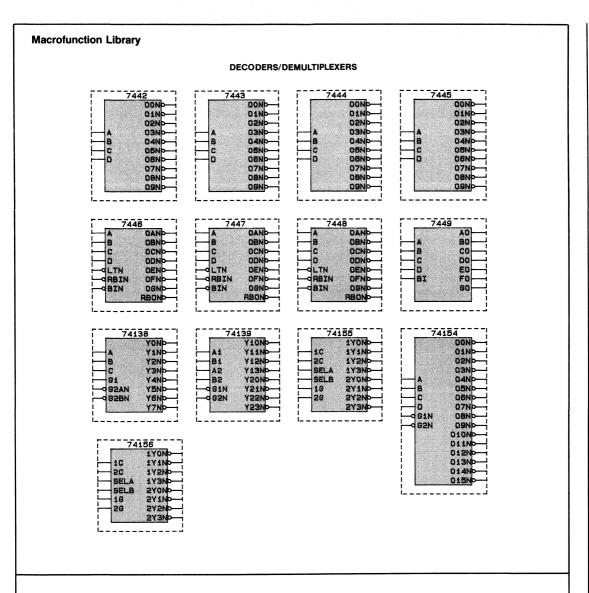

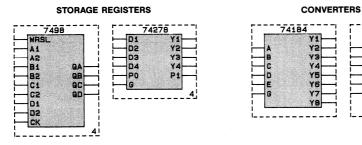

#### **MACROFUNCTIONS**

MacroFunctions, shown in Fig. 3, allow the circuit designer to use popular TTL SSI and MSI building blocks. Many MacroFunctions are standard TTL circuits such as counters, comparators, multiplexers, decoders, shift registers, etc. and are identified by their familiar TTL part numbers. MacroFunctions are constructed by combining one or more Macrocells.

These high-level function blocks may be combined with low-level gate and flipflop elements to produce a complete logic design.

An automatic function built into the A+PLUS CAD software ensures that the use of MacroFunctions causes no loss of design efficiency. A+PLUS analyzes the complete logic schematic and automatically removes unused gates and flip-flops from any MacroFunction employed. This "MacroMunching" process allows the logic designer to employ MacroFunctions without the headaches of optimizing their use.

All inputs to MacroFunctions are designed with "intelligent" default input signal levels (VCC or GND). Normally active high and low signals or unused inputs can simply be left unconnected . . . further improving productivity and reducing the burden placed on the designer.

### **DESIGN LIBRARIES**

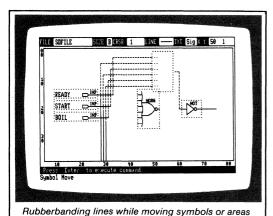

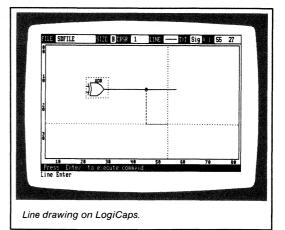

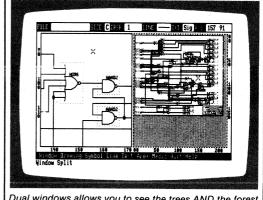

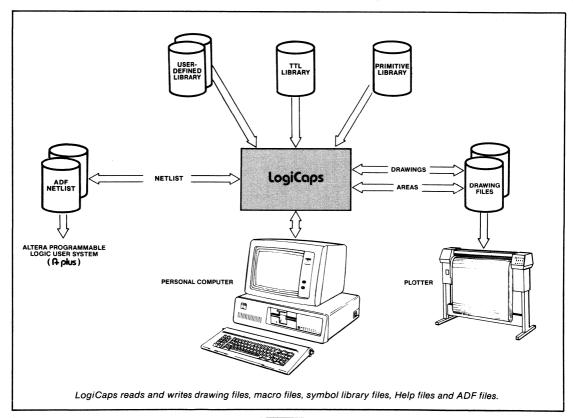

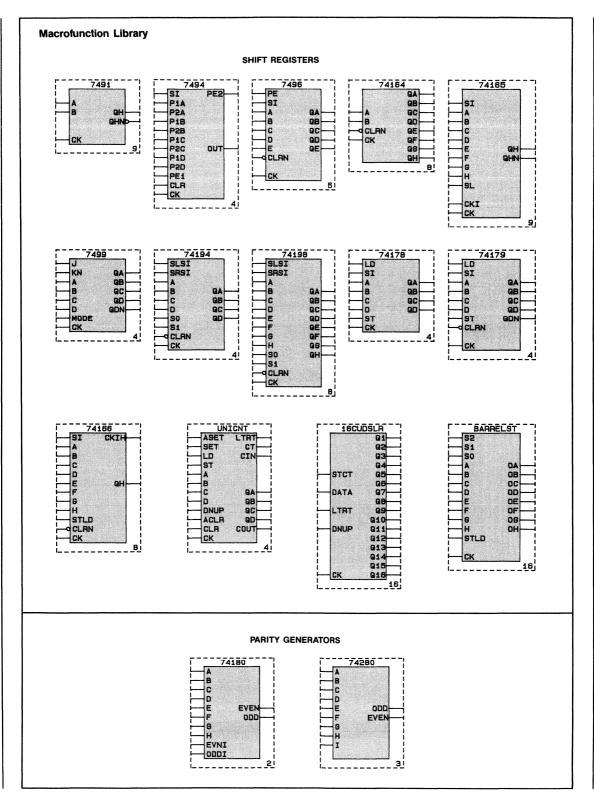

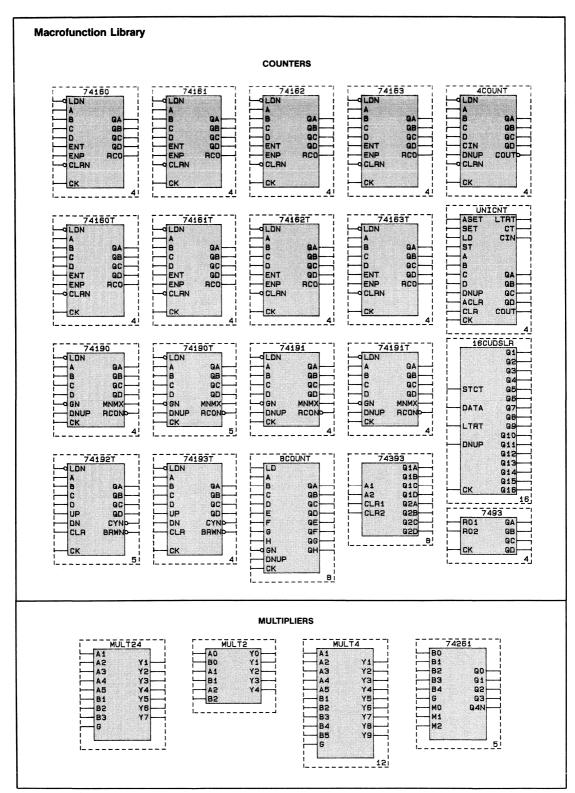

Altera provides both a Primitive and MacroFunction library. These libraries are used with Altera's LogiCaps schematic capture design entry to specify the logic. Elements from both libraries may be used in the same design, allowing full utilization of the EP1810 resources. The Primitive library is included with LogiCaps software package. The MacroFunction library, PLSLIB-TTL, is avaliable as an option.

#### Figure 3. MacroFunction Symbol

MacroFunctions are TTL compatible SSI and MSI circuits giving the circuit designer a high-level approach to EPLD design. MacroFunctions include input default values to unconnected inputs and "MacroMunching" to unused outputs. Altera's MacroFunction library consists of over 100 components.

### 74162 FUNCTION TABLE

|    |     |      | INPL | JTS |   |   |   |   | OUTPUTS |         |         |       |     |

|----|-----|------|------|-----|---|---|---|---|---------|---------|---------|-------|-----|

| СК | LDN | CLRN | ENP  | ENT | D | С | В | Α | $Q_D$   | $Q_{C}$ | $Q_{B}$ | $Q_A$ | RCO |

| Г  | Х   | L    | Х    | Х   |   |   |   |   | L       | L       | L       | L     | L   |

| 1  | L   | Н    | Х    | Х   | d | С | b | a | d       | С       | b       | a     | L   |

| 1  | Н   | Н    | Х    | L   |   |   |   |   | H       | DLD (   | COU     | NΤ    | L   |

| 1  | Н   | Н    | L    | Х   |   |   |   |   | H       | OLD (   | 1000    | NΤ    | L   |

| ı  | Н   | Н    | Н    | Н   |   |   |   |   | (       | COUN    | IT UF   | >     | L   |

| ı  | Н   | Н    | Н    | Н   |   |   |   |   | Н       | L       | L       | Н     | Н   |

- H = high level (steady state)

- L = low level (steady state)

- X = don't care (any input including transitions)

- a,b,c,d = level of steady state input at inputs A,B,C,D

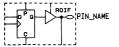

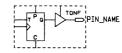

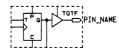

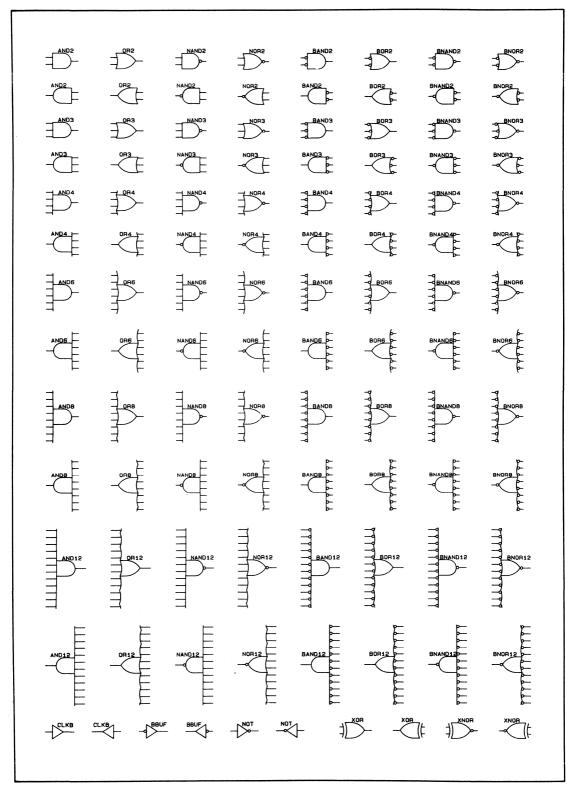

#### PRIMITIVE LIBRARY

The Primitive library consists of 80 low-level logic gates, flip-flop, and I/O symbols. See PLE40 data sheet. Basic gates provided are AND, OR, NAND, NOR, Exclusive OR and NOR, and NOT functions. De-Morgan's inversion (bubble input) of each gate is also included. These logic gates have a maximum of 12 inputs. Larger gates may be constructed by chaining primitives together. Flip-flops in the form of D, T, JK, and SR types are supplied. Each flip-flop has asynchronous clear capability. To connect signals to external pins, input and tri-state I/O buffers are available. For the designer's convenience, "compound primitives" which combine register and I/O buffers are also supplied.

#### **MACROFUNCTION LIBRARY**

Altera's MacroFunction library encompasses over 100 high-level building blocks that can greatly in-

crease design productivity. See PLSLIB-TTL data sheet. The library contains the most commonly used TTL SSI and MSI functions. In addition, a number of more specialized MacroFunctions have been added. These blocks perform logic functions in an optimum manner for EPLD implementation. They include counters implemented with toggle flip-flops, inhibit gates, combinational shift-registers/counters and a variety of useful logic structures not found in standard TTL devices.

### STARTING A DESIGN

To get started on an EP1810 design the following sequence of preliminary steps is suggested. The equations given will help estimate how to build your system with EP1810's.

#### **PARTITIONING**

First, partition the complete system into functional blocks. Major functional blocks may be expressed in standard MSI TTL form for integration within the EP1810. Should the design require a multiple EPLD solution, the I/O connections which interface between the EPLDs should be minimized. The complete schematic should be structured as a set of subsystems such as counters, shift-registers, comparators, etc., to allow easy design entry.

#### **TIMING SPECIFICATIONS**

Knowledge of the base clock frequency and critical timing paths are necessary to make the correct choice of EPLDs. The EP1810 series can support circuits operating up to 33 MHz. Critical timing paths are determined based upon input buffer, logic array, and output buffer delays. (Refer to AC characteristics). Smaller EPLDs, such as the EP910 or EP610, can be used for circuitry that demand higher speed requirements on critical paths.

#### **ESTIMATING A FIT**

To estimate the amount of logic which will fit into an EP1810, the number of input and output pins, and the number of Macrocells must be specified.

To estimate the number of Macrocells, determine; (a) the number of buried flip-flops (flip-flops which do not drive output pins), and (b) the number of Macrocells used by MacroFunctions. Since basic gates are implemented within the Logic Array, in most instances they do not require an entire Macrocell, thus they may be safely ignored in the estimation.

Each member of the MacroFunction library has a maximum number of Macrocells used to build the function. This number is shown in the lower right hand corner of the symbol. Refer to Figures 3 and 12 to determine how many Macrocells each Macro-Function requires. Note that some MacroFunctions have no Macrocell specification. These functions use only a portion of the logic array, thus other logic could be added before the entire Macrocell is used.

#### **Estimation Formula:**

- (a) Determine the number of output pins = OP

- (b) Determine the number of input pins = IP (if less than 16 enter zero)

- (c) Determine the number of Macrocells = BFF + MR where BFF = Buried Flip-Flops and MR = MacroFunction Requirements

If OP + IP + BFF + MR < 48 the design will most likely fit into an EP1810. Complete the design using Altera's LogiCaps and A+PLUS CAD tools.

### **DESIGN SECURITY**

The EP1810 contains a programmable design security feature that controls the access to the data programmed into the device. If this programmable feature is used, a proprietary design implemented in the device cannot be copied nor retrieved. This enables a high level of design control to be obtained since programmed data within EPROM cells is invisible. The bit that controls this function, along with all other program data, may be reset simply by erasing the device.

T<sub>AMB</sub>

### **ABSOLUTE MAXIMUM RATINGS**

Note: See Design Recommendations

| SYMBOL           | PARAMETER                         | CONDITIONS                      | MIN  | MAX  | UNIT |

|------------------|-----------------------------------|---------------------------------|------|------|------|

| V <sub>CC</sub>  | Supply voltage                    | 147.1                           | -2.0 | 7.0  | ٧    |

| V <sub>PP</sub>  | Programming supply voltage        | With respect<br>to GND note (3) | -2.0 | 13.5 | ٧    |

| Vı               | DC INPUT voltage                  | to divid fiote (3)              | -2.0 | 7.0  | ٧    |

| I <sub>MAX</sub> | DC V <sub>CC</sub> or GND current |                                 | -300 | +300 | mA   |

| Гоит             | DC OUTPUT current, per pin        |                                 | -25  | +25  | mA   |

| Pn               | Power dissipation                 | -                               |      | 1500 | mW   |

No bias

Under bias

COMMERCIAL, INDUSTRIAL, MILITARY

+150

+135

-65

-65

**OPERATING RANGES**

°C

°C

### RECOMMENDED OPERATING CONDITIONS

Storage temperature

Ambient temperature

| SYMBOL          | PARAMETER             | CONDITIONS     | MIN        | MAX             | UNIT |

|-----------------|-----------------------|----------------|------------|-----------------|------|

| V <sub>CC</sub> | Supply Voltage        | note (6)       | 4.75 (4.5) | 5.25 (5.5)      | V    |

| V <sub>I</sub>  | INPUT voltage         |                | 0          | V <sub>CC</sub> | V    |

| V <sub>0</sub>  | OUTPUT voltage        |                | 0          | V <sub>CC</sub> | V    |

| TA              | Operating temperature | For Commercial | 0          | 70              | °C   |

| TA              | Operating temperature | For Industrial | -40        | 85              | °C   |

| T <sub>C</sub>  | Case temperature      | For Military   | -55        | 125             | °C   |

| T <sub>R</sub>  | INPUT rise time       | note (9)       |            | 100             | ns   |

| T <sub>F</sub>  | INPUT fall time       | note (9)       |            | 100             | ns   |

### DC OPERATING CHARACTERISTICS

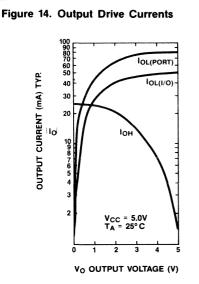

(V<sub>CC</sub> = 5V  $\pm$  5%, T<sub>A</sub> = 0°C to 70°C for Commercial) (V<sub>CC</sub> = 5V  $\pm$  10%, T<sub>A</sub> = -40°C to 85°C for Industrial) (V<sub>CC</sub> = 5V  $\pm$  10%, T<sub>C</sub> = -55°C to 125°C for Military)\*

Note (1) and (6)

| SYMBOL           | PARAMETER                                  | CONDITIONS                                                                  | MIN  | TYP | MAX                   | UNIT |

|------------------|--------------------------------------------|-----------------------------------------------------------------------------|------|-----|-----------------------|------|

| V <sub>IH</sub>  | HIGH level input voltage                   |                                                                             | 2.0  |     | V <sub>CC</sub> + 0.3 | ٧    |

| V <sub>IL</sub>  | LOW level input voltage                    |                                                                             | -0.3 |     | 0.8                   | V    |

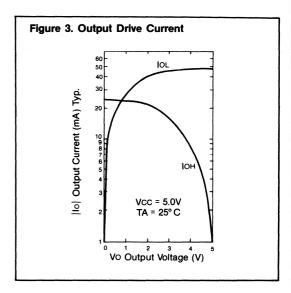

| V <sub>OH</sub>  | HIGH level TTL output voltage              | I <sub>OH</sub> = -4mA DC                                                   | 2.4  |     |                       | ٧    |

| V <sub>OH</sub>  | HIGH level CMOS output voltage             | I <sub>OH</sub> = -2mA DC                                                   | 3.84 |     |                       | ٧    |

| V <sub>OL</sub>  | LOW level output voltage                   | I <sub>OL</sub> = 4mA DC                                                    |      |     | 0.45                  | ٧    |

| l <sub>l</sub>   | Input leakage current                      | V <sub>I</sub> = V <sub>CC</sub> or GND                                     | -10  |     | +10                   | μΑ   |

| I <sub>OZ</sub>  | 3-state output off-state current           | V <sub>0</sub> = V <sub>CC</sub> or GND                                     | -10  | -   | +10                   | μΑ   |

| I <sub>CC1</sub> | V <sub>CC</sub> supply current (standby)   | V <sub>I</sub> = V <sub>CC</sub> or GND<br>No load                          |      | 35  | 150                   | μΑ   |

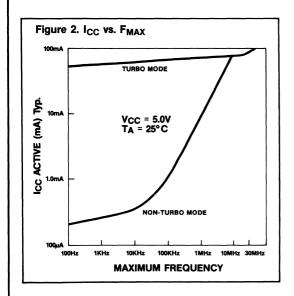

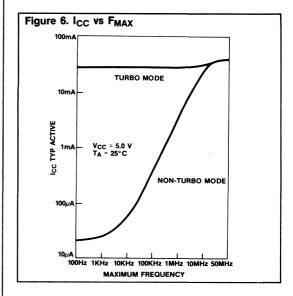

| I <sub>CC2</sub> | V <sub>CC</sub> supply current (non-turbo) | V <sub>I</sub> = V <sub>CC</sub> or GND<br>No load, f = 1.0 MHz<br>note (7) |      | 45  | :                     | mA   |

| I <sub>CC3</sub> | V <sub>CC</sub> supply current (turbo)     | V <sub>I</sub> = V <sub>CC</sub> or GND<br>No load, f = 1.0 MHz<br>note (7) |      | 120 |                       | mA   |

### CAPACITANCE

Note (4)

| SYMBOL           | PARAMETER             | CONDITIONS                           | MIN | MAX | UNIT |

|------------------|-----------------------|--------------------------------------|-----|-----|------|

| C <sub>IN</sub>  | Input Capacitance     | V <sub>IN</sub> = 0V<br>f = 1.0 MHz  |     | 20  | pF   |

| C <sub>OUT</sub> | Output Capacitance    | V <sub>OUT</sub> = 0V<br>f = 1.0 MHz |     | 20  | pF   |

| C <sub>CLK</sub> | Clock Pin Capacitance | V <sub>IN</sub> = 0V<br>f = 1.0 MHz  |     | 25  | pF   |

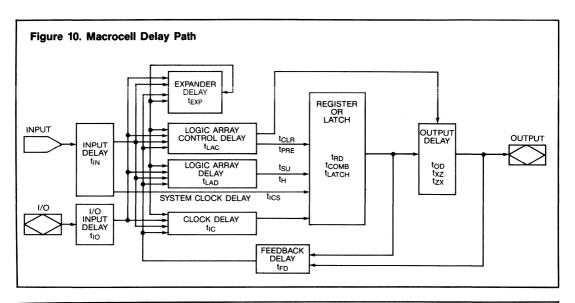

### **AC CHARACTERISTICS**

(V<sub>CC</sub> = 5V  $\pm$  5%, T<sub>A</sub> = 0°C to 70°C for Commercial) (V<sub>CC</sub> = 5V  $\pm$  10%, T<sub>A</sub> = -40°C to 85°C for Industrial) (V<sub>CC</sub> = 5V  $\pm$  10%, T<sub>C</sub> = -55°C to 125°C for Military)\*

|                  |                                                                                       |                                  | E   | P1810-4 | 15  | E   | P1810-5 | i5  | NON-TURBO<br>Adder |      |

|------------------|---------------------------------------------------------------------------------------|----------------------------------|-----|---------|-----|-----|---------|-----|--------------------|------|

| SYMBOL           | PARAMETER                                                                             | CONDITIONS                       | MIN | TYP     | MAX | MIN | TYP     | MAX | note (5)           | UNIT |

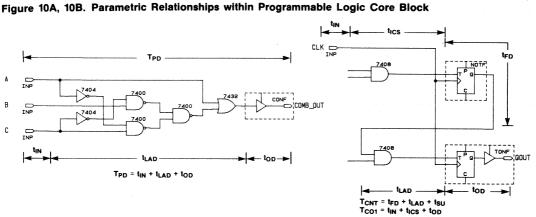

| t <sub>PD1</sub> | Input to non-registered output                                                        | C = 25°5                         |     |         | 45  |     |         | 55  | 30                 | ns   |

| t <sub>PD2</sub> | I/O input to non-registered output                                                    | $C_1 = 35pF$                     |     |         | 50  |     |         | 60  | 30                 | ns   |

| t <sub>iN</sub>  | Input pad and buffer delay                                                            |                                  |     | 8       |     |     | 10      |     | 0                  | ns   |

| t <sub>IO</sub>  | I/O input pad and buffer delay                                                        |                                  |     | 5       |     |     | 5       |     | 0                  | ns   |

| t <sub>LAD</sub> | Logic Array delay                                                                     |                                  |     | 25      |     |     | 30      |     | 30                 | ns   |

| t <sub>OD</sub>  | Output buffer and pad delay                                                           | 0 - 05-5                         |     | 12      | .,  |     | 15      |     | 0                  | ns   |

| t <sub>ZX</sub>  | Output buffer enable                                                                  | C <sub>1</sub> = 35pF            |     | 12      |     |     | 15      |     | 0                  | ns   |

| t <sub>XZ</sub>  | Output buffer disable                                                                 | C <sub>1</sub> = 5pF<br>note (2) |     | 12      |     |     | 15      |     | 0                  | ns   |

| f <sub>max</sub> | Maximum clock frequency                                                               | note (10)                        |     | 33.3    |     |     | 28.6    |     | 0                  | MHz  |

| t <sub>SU</sub>  | Register set-up time                                                                  |                                  |     | 13      |     |     | 16      |     | 0                  | ns   |

| t <sub>HS</sub>  | Register hold time (system clock)                                                     |                                  |     | 0       |     |     | 0       |     | 0                  | ns   |

| t <sub>H</sub>   | Register hold time                                                                    |                                  |     | 18      |     |     | 23      |     | 0                  | ns   |

| t <sub>CH</sub>  | Clock high time                                                                       |                                  |     | 17      |     |     | 20      |     | 0                  | ns   |

| t <sub>CL</sub>  | Clock low time                                                                        |                                  |     | 17      |     |     | 20      |     | 0                  | ns   |

| t <sub>IC</sub>  | Clock delay                                                                           |                                  |     | 25      |     |     | 30      |     | 30                 | ns   |

| t <sub>ICS</sub> | System clock delay                                                                    |                                  |     | 5       |     |     | 7       |     | 0                  | ns   |

| t <sub>FD</sub>  | Feedback delay                                                                        |                                  |     | 2       |     |     | 4       |     | -30                | ns   |

| t <sub>CLR</sub> | Register clear delay                                                                  |                                  |     | 30      |     |     | 35      |     | 30                 | ns   |

| t <sub>CNT</sub> | Minimum clock period (register<br>output feedback to register<br>input-internal data) |                                  |     | 40      |     |     | 50      |     | 0                  | ns   |

| f <sub>CNT</sub> | Internal maximum frequency<br>(1/t <sub>CNT</sub> )                                   | note (7)                         |     | 25      |     |     | 20      |     | 0                  | MHz  |

#### Notes:

Typical values are for  $T_A = 25$ °C,  $V_{CC} = 5V$

Sample tested only for an output change of 500mV.

- Minimum DC input is -0.3V. During transitions, the inputs may undershoot to -2.0V for periods less than 20ns.

- 4. Capacitance measured at 25°C. Sample tested only. Clock pin capacitance for dedicated clock inputs only. Pin 19, (high voltage pin during programming), has capacitance of 160 pF max. See TURBO-BIT\*, page 19.

- 6. Figures in ( ) pertain to military and industrial temperature

- Measured with device programmed as four 12-Bit counters.

- 8. EPLD automatically goes into standby mode if logic transitions do not occur when in non-turbo mode (approximately 100 ns after last transition).

- 9. Clock  $t_r$ ,  $t_f$  = 100ns (50ns). 10. The  $f_{\text{MAX}}$  values shown represent the highest frequency for pipelined data.

These are typical values derived from design simulations. Call Altera Applications for the most recent values. (408) 984-2805 x102.

| GRADE                         | AVAILABILITY        |

|-------------------------------|---------------------|

| Commercial<br>(0°C to 70°C)   | EP1810-45 EP1810-55 |

| Industrial<br>(-40°C to 85°C) | Consult Factory     |

| Military<br>(-55°C to 125°C)  | Consult Factory     |

<sup>\*</sup>The specifications noted above apply to military operating range devices. MIL-STD-883 compliant product applications are provided in military product drawings available on request from Altera marketing at 408/984-2805, ext. 101. These military product drawings should be used for the preparation of source control drawings.

#### **FUNCTIONAL TESTING**

The EP1810 is fully functionally tested and guaranteed through complete testing of each programmable EPROM bit and all internal logic elements thus ensuring 100% programming yield.

The erasable nature of the EP1810 allows test programs to be used and then erased during early stages of the production flow. This facility to use application-independent, general purpose tests is called generic testing and is unique among user-defined LSI logic devices. The devices also contain on board test circuitry to allow verification of a function and AC specification once encapsulated in non-window packages.

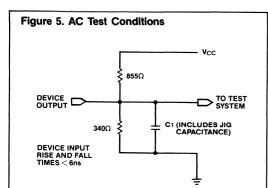

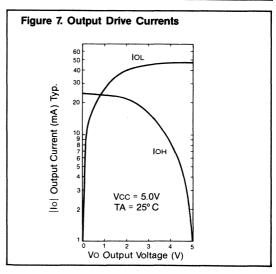

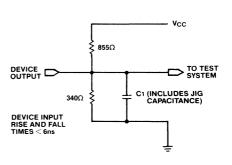

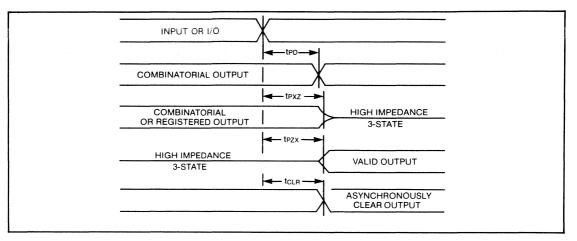

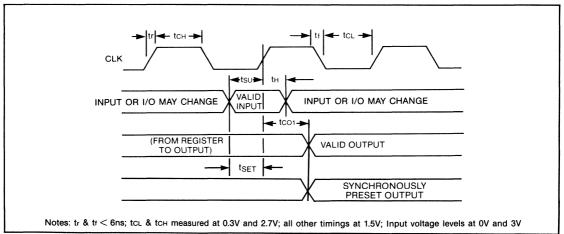

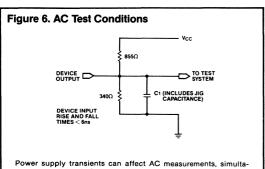

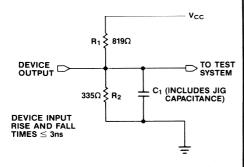

Power supply transients can affect AC measurements, simultaneous transitions of multiple outputs should be avoided for accurate measurement. Do not attempt to perform threshold tests under AC conditions. Large amplitude, fast ground current transients normally occur as the device outputs discharge the load capacitances. These transients flowing through the parasitic inductance between the device ground pin and the test system ground can create significant reductions in observable input noise immunity.

### **TURBO-BIT**

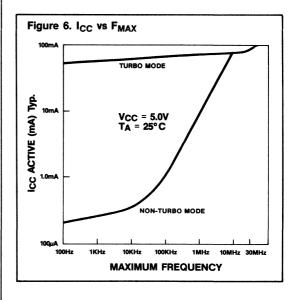

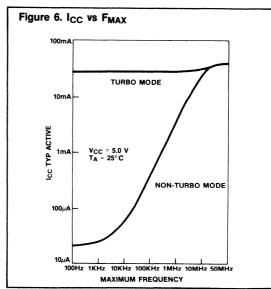

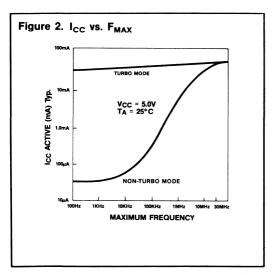

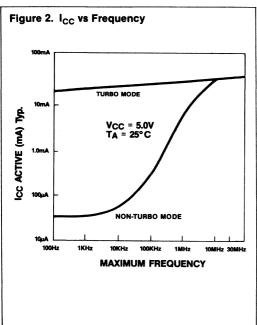

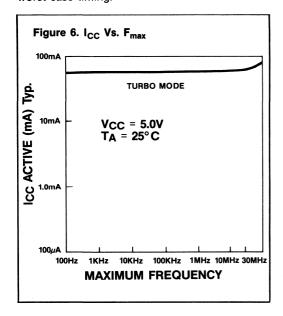

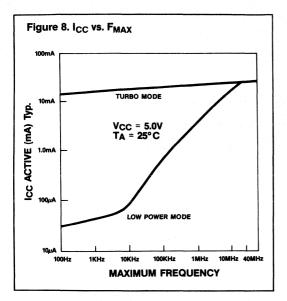

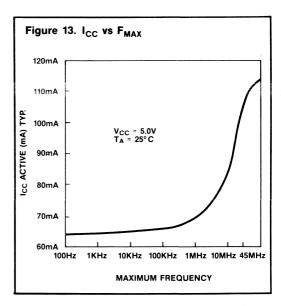

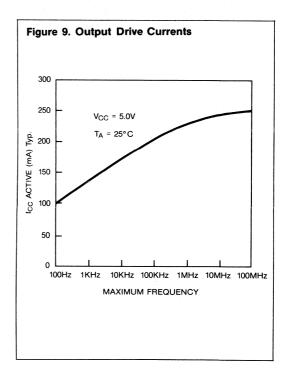

Some EPLDs contain a programmable option to control the automatic power down feature that enables the low standby power mode of the device. This option is controlled by a TURBO-BIT which can be set using A+PLUS. When the TURBO-BIT is programmed (Turbo = ON), the low standby power mode (lcc1) is disabled. This renders the circuit less sensitive to Vcc noise transients which can be created by the power-up/power-down cycle when operating in the low power mode. The typical lcc vs frequency data for both Turbo and Non-Turbo (low power) mode is shown in each EPLD data sheet. All AC values are tested with the TURBO-BIT programmed.

If the design requires low power operation then the TURBO-BIT should be disabled (Turbo = OFF). When operating in this mode, some AC parameters are subject to increase. Values given in the AC specifications section under "Non-Turbo Adder" must be added to the respective AC parameter to determine worst-case timing.

### **PGA CONNECTION DIAGRAM**

### **FEATURES**

- High density, User-Configurable LSI logic replacement for conventional and custom logic

- Functional and pin compatible with the Altera EP1810

- 20 MHz clock rates

- "Zero Power" (typically 35 μA standby)

- 48 Macrocells with configurable I/O architecture allowing 64 inputs or 48 outputs

- Programmable registers providing D, T, SR or JK flipflops with individual Asynchronous Clear control.

- Programmable clock option allows independent clocking of all registers

- TTL/CMOS I/O compatibility

- 100% generically testable—provides 100% programming yield

- Programmable "Security Bit" allows total protection of proprietary designs

- CAD support from Altera's A+PLUS Development System featuring schematic capture design entry with extensive Primitive and TTL libraries

- Package in a 68 pin (window) and plastic (one time programmable) JLCC, PLCC and PGA configurations

### CONNECTION DIAGRAM

### GENERAL DESCRIPTION

The Altera EP1800 is a pin-compatible version of the popular EP1810 Erasable Programmable Logic Device (EPLD). Available in 68-pin PGA and 68-pin J-leaded chip carrier packages, the EP1800 contains 48 Macrocells with user-configurable I/O architecture, allowing up to 64 inputs and 48 outputs.

Each of the 48 Macrocells contains a programmable AND and fixed OR PLA structure, see EP1810 datasheet, with a maximum of eight product terms for logic implementation. In addition, single product terms control Output Enable/ Asynchronous Clock and Asynchronous Clear functions.

The Altera proprietary programmable I/O architecture allows the EP1800 user to program output and feedback paths for both combinatorial or registered operation, active high or active low.

For increased flexibility, the EP1800 also includes programmable registers. Each of the 48 internal registers may be programmed to be D, T, SR or JK flipflop. In addition, each register may be clocked asynchronously on an individual basis or synchronously on a banked register basis.

For proper operation, standard high performance design practices should be followed. It is recommended that opaque labels be placed over device window. Input and output pins must be constrained to the range GND  $\leq (V_{IN} \text{ or } V_{OUT}) \leq V_{CC}.$  Unused inputs must always be tied to an appropriate logic level (e.g. either  $V_{CC}$  or GND). Each set of  $V_{CC}$  and GND pins must be shorted together directly at the device. Power supply decoupling capacitors of at least  $.2\mu F$  must be connected between each  $V_{CC}$  pin and GND. For the most effective decoupling, connect one capacitor between each set of  $V_{CC}$  and GND pins, directly at the device.

Programming the EP1800 is accomplished by using the Altera A+PLUS PC-based development software which supports schematic capture, netlist, state machine and Boolean equation design entry methods. Once the design is entered, A+PLUS automatically performs translation into logical equations, Boolean minimization, and design fitting directly to an EP1800. The device may then be programmed to acheive customized working silicon within minutes at the designer's own desktop.

For full EP1800 functional description please consult the EP1810 datasheet.

Note: See Design Recommendations

| SYMBOL           | PARAMETER                         | CONDITIONS                      | MIN  | MAX  | UNIT |

|------------------|-----------------------------------|---------------------------------|------|------|------|

| V <sub>CC</sub>  | Supply voltage                    | NAC'AL                          | -2.0 | 7.0  | V    |

| V <sub>PP</sub>  | Programming supply voltage        | With respect<br>to GND note (3) | -2.0 | 13.5 | V    |

| Vi               | DC INPUT voltage                  | - to divid note (5)             | -2.0 | 7.0  | V    |

| I <sub>MAX</sub> | DC V <sub>CC</sub> or GND current |                                 | -300 | +300 | mA   |

| l <sub>out</sub> | DC OUTPUT current, per pin        |                                 | -25  | +25  | mA   |

| $P_D$            | Power dissipation                 |                                 |      | 1500 | mW   |

| T <sub>STG</sub> | Storage temperature               | No bias                         | -65  | +150 | °C   |

| T <sub>AMB</sub> | Ambient temperature               | Under bias                      | -65  | +135 | °C   |

### RECOMMENDED OPERATING CONDITIONS

| SYMBOL          | PARAMETER             | CONDITIONS     | MIN        | MAX             | UNIT |

|-----------------|-----------------------|----------------|------------|-----------------|------|

| V <sub>CC</sub> | Supply Voltage        | note (6)       | 4.75 (4.5) | 5.25 (5.5)      | ٧    |

| VI              | INPUT voltage         |                | 0          | V <sub>CC</sub> | ٧    |

| V <sub>0</sub>  | OUTPUT voltage        |                | 0          | V <sub>CC</sub> | ٧    |

| TA              | Operating temperature | For Commercial | 0          | 70              | °C   |

| TA              | Operating temperature | For Industrial | -40        | 85              | °C   |

| T <sub>C</sub>  | Case temperature      | For Military   | -55        | 125             | °C   |

| T <sub>R</sub>  | INPUT rise time       | note (9)       |            | 500             | ns   |

| T <sub>E</sub>  | INPUT fall time       | note (9)       |            | 500             | ns   |

### DC OPERATING CHARACTERISTICS

(V<sub>CC</sub> = 5V  $\pm$  5%, T<sub>A</sub> = 0°C to 70°C for Commercial) (V<sub>CC</sub> = 5V  $\pm$  10%, T<sub>A</sub> = -40°C to 85°C for Industrial) (V<sub>CC</sub> = 5V  $\pm$  10%, T<sub>C</sub> = -55°C to 125°C for Military)\*

Note (1) and (6)

| SYMBOL           | PARAMETER                                  | CONDITIONS                                                                  | MIN  | TYP | MAX                   | UNIT |

|------------------|--------------------------------------------|-----------------------------------------------------------------------------|------|-----|-----------------------|------|

| V <sub>IH</sub>  | HIGH level input voltage                   |                                                                             | 2.0  |     | V <sub>CC</sub> + 0.3 | ٧    |

| V <sub>IL</sub>  | LOW level input voltage                    |                                                                             | -0.3 |     | 0.8                   | ٧    |

| V <sub>OH</sub>  | HIGH level TTL output voltage              | I <sub>OH</sub> = -4mA DC                                                   | 2.4  |     |                       | ٧    |

| V <sub>OH</sub>  | HIGH level CMOS output voltage             | I <sub>OH</sub> = -2mA DC                                                   | 3.84 |     |                       | ٧    |

| V <sub>OL</sub>  | LOW level output voltage                   | I <sub>OL</sub> = 4mA DC                                                    |      |     | 0.45                  | ٧    |

| I <sub>1</sub>   | Input leakage current                      | V <sub>I</sub> = V <sub>CC</sub> or GND                                     | -10  |     | +10                   | μΑ   |

| I <sub>OZ</sub>  | 3-state output off-state current           | $V_0 = V_{CC}$ or GND                                                       | -10  |     | +10                   | μΑ   |

| I <sub>CC1</sub> | V <sub>CC</sub> supply current (standby)   | V <sub>I</sub> = V <sub>CC</sub> or GND<br>No load                          |      | 35  | 150                   | μΑ   |

| I <sub>CC2</sub> | V <sub>CC</sub> supply current (non-turbo) | V <sub>I</sub> = V <sub>CC</sub> or GND<br>No load, f = 1.0 MHz<br>note (7) |      | 15  | 30 (40)               | mA   |

| I <sub>CC3</sub> | V <sub>CC</sub> supply current (turbo)     | V <sub>I</sub> = V <sub>CC</sub> or GND<br>No load, f = 1.0 MHz<br>note (7) |      | 90  | 140 (180)             | mA   |

### CAPACITANCE

### Note (4)

| SYMBOL           | PARAMETER             | CONDITIONS                           | MIN | MAX | UNIT |

|------------------|-----------------------|--------------------------------------|-----|-----|------|

| C <sub>IN</sub>  | Input Capacitance     | V <sub>IN</sub> = 0V<br>f = 1.0 MHz  |     | 15  | pF   |

| C <sub>OUT</sub> | Output Capacitance    | V <sub>OUT</sub> = 0V<br>f = 1.0 MHz |     | 15  | pF   |

| C <sub>CLK</sub> | Clock Pin Capacitance | V <sub>IN</sub> = 0V<br>f = 1.0 MHz  |     | 25  | pF   |

$(V_{CC}$  = 5V  $\pm$  5%,  $T_A$  = 0°C to 70°C for Commercial)  $(V_{CC}$  = 5V  $\pm$  10%,  $T_A$  = -40°C to 85°C for Industrial)  $(V_{CC}$  = 5V  $\pm$  10%,  $T_C$  = -55°C to 125°C for Military)\*

|                  |                                                                                 |                                  | EP1  | 800-2 | EP18 | 300-3 | EPI  | 800 | NON-TURBO<br>Adder |      |

|------------------|---------------------------------------------------------------------------------|----------------------------------|------|-------|------|-------|------|-----|--------------------|------|

| SYMBOL           | PARAMETER                                                                       | CONDITIONS                       | MIN  | MAX   | MIN  | MAX   | MIN  | MAX | note (5)           | UNIT |

| t <sub>PD1</sub> | Input to non-registered output                                                  | C = F0=F                         |      | 65    |      | 75    |      | 85  | 30                 | ns   |

| t <sub>PD2</sub> | I/O input to non-registered output                                              | C <sub>1</sub> = 50pF            |      | 70    |      | 80    |      | 90  | 30                 | ns   |

| t <sub>IN</sub>  | Input pad and buffer delay                                                      |                                  |      | 10    |      | 12    |      | 14  | 0                  | ns   |

| t <sub>IO</sub>  | I/O input pad and buffer delay                                                  |                                  |      | 5     |      | 5     |      | 5   | 0                  | ns   |

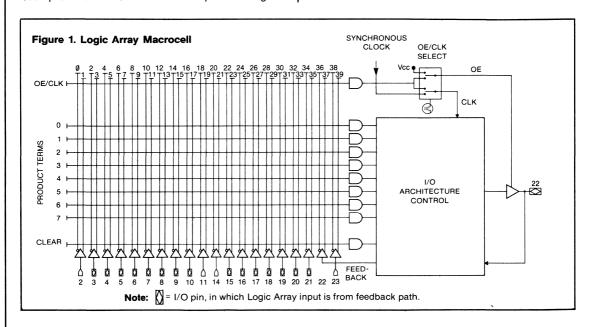

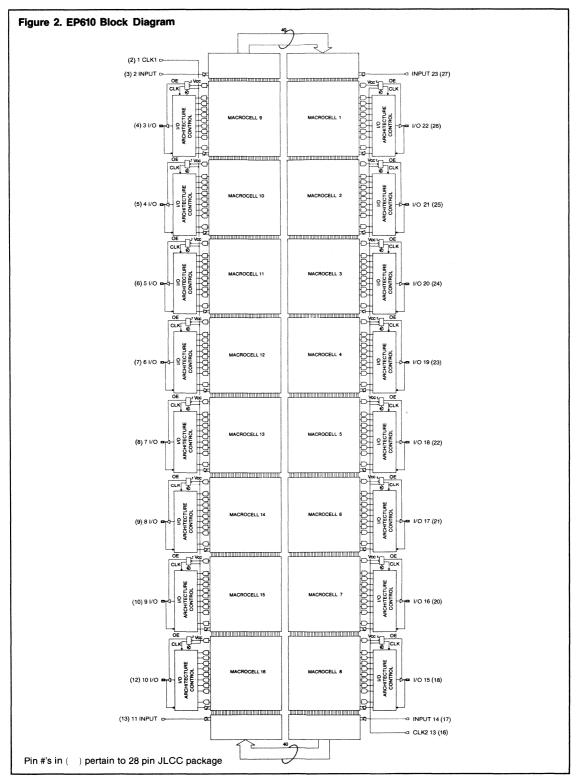

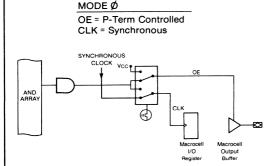

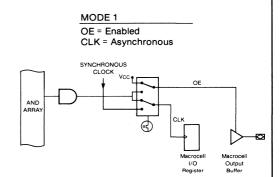

| t <sub>LAD</sub> | Logic Array delay                                                               |                                  |      | 40    |      | 44    |      | 48  | 30                 | ns   |